- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

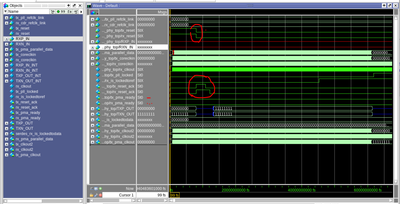

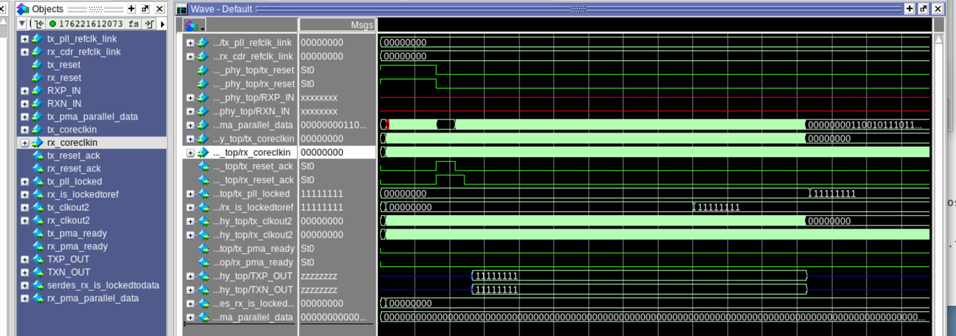

I build my controller model to Agilex F-tile transceiver. Please see the configuration below for F-tile and simulation waveform. Xcvr is asserting tx_reset/tx_reset_ack and rx_reset/rx_reset_ack and completing the reset sequence. But it is not asserting tx_ready. I used support logic generated by Quartus flow (6.7 user's guide). My configuration is also RX de-skew disabled.

I could not find any reason not to getting tx_ready. Could you please help if anyone knows the answer please let me know. I am stuck at this point. In the waveform tx_ready mapped to tx_pma_ready and rx_ready mapped rx_pma_ready.

Thanks

Mesbah

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Can you please check are you fulfilling the reset signal requirements? Please refer below link.

Also, tx_reset and rx_reset input for TX/RX PMAs and TX/RX datapath. Must be kept asserted until tx_reset_ack and rx_reset_ack is asserted. Applies to all TX/RX channels in a F-Tile PMA/FEC Direct PHY Intel® FPGA IP instance.

Can you please clarify which Run-Time Reset Sequence you are following.

- 3.8.6. Run-time Reset Sequence—TX

- 3.8.7. Run-time Reset Sequence—RX

- 3.8.8. Run-time Reset Sequence—TX + RX

- 3.8.9. Run-time Reset Sequence—TX with FEC

Thank you

Kshitij Goel

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Do we have any update on this?

Thank you

Kshitij Goel

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi K**bleep**ij,

Thank you for your quick response. Yes, I fulfilled the reset sequence that was described in 6.7. I am getting tx_reset_ack/rx_reset_ack, tx_pll_locked and rx_is_lockedtoref but not tx_ready/rx_ready. that I mentioned before.

I also noticed that when tx_pll_locked is asserted, tx_clkout2 stop toggling. Please look at the at the waveform again, the run-time reset sequence is following as indicated in 3.8.8 except asserting tx_ready/rx_ready

I am using Questasim simulator. I am using FAST_SIM directive. Please let me know, if I am missing something.

Appreciate your response. I am still stuck at this point.

Thanks

Mesbah

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Sorry K**bleep**ij for the typo in your name,

Thanks

Mesbah

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Sorry again K**bleep**ij,

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Are you getting tx_reset_ack and rx_reset_ack?

tx_ready will assert when TX PMA and TX datapath are reset successfully and ready for data transfer.

and rx_ready will assert when RX PMA and RX datapath are reset successfully and ready for data transfer, If RX de-skew is disabled.

Note: During F-Tile link initialization, the data pattern sent from the TX has to be scrambled to get rx_ready to assert. If a 0101 pattern or other constant patterns are sent, rx_ready does not assert, and the link does not initialize.

tx_ready and rx_ready will assert when reset has been done successfully.

Thank you

Kshitij Goel

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Goel,

Yes, I am getting tx_reset_ack and rx_reset_ack.

Could please clarify Red bold part. I am getting tx_reset_ack/rx_reset_ack. Does not it mean TX PMA and TX data path are reset successfully?

tx_ready will assert when TX PMA and TX datapath are reset successfully and ready for data transfer

I am going to run with TX scrambled data pattern to see rx_ready

Thanks

Mesbah

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Can you please generate an example design and take a reference of it.

If you still face issue please let me know.

Thank you

Kshitij Goel

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Goel,

I am using latest released Quartus version 22.4. I can generate only example design of "FHT NRZ 25G 1 PMA lane RSFEC 272/258"

My configuration is closer to "FGT NRZ 50G 2 PMA lanes RSFEC 528/514" but could not run as it did generate support_logic.

My configuration is "FGT NRZ 25G 8 PMA lanes." without RSFEC

Thanks

Mesbah

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Sorry, typo it did not generate support_logic

Thanks

Mesbah

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Mesbah,

Can you please share your project, so that I can look into the issue.

Thank you

Kshitij Goel

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Goel,

Sorry for the late response. I was waiting for Quartus 23.1 to release and use it We just received it and IT is i

Do you want whole project? I sent you the F-Tile configuration. My project includes our IP blocks.

This is not loopback model. Our IP has also Serdes. This is a communication between to Serdes.

We want F-Tile transceiver is ready to communicate with another Serdes. Do you have any example design of that configuration that I mentioned in my first correspondence? even loopback is also fine. Please share with me. Quartus project have a few example_design. I can not configure with my configuration and generate example design. If you have please share with me

Thanks

Mesbah

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I'm experiencing this same symptom. I have created another thread with details because I suspect this discussion is dead.

Bumpity, bump.

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page