- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Intel team,

I'm having a 2 socket machine and wanted to bind all ranks to the same socket. I found a variable I_MPI_PIN_PROCESSOR_LIST in the below Intel documentation. However, when I try to use that I don't see an expected behavior.

I wanted to understand what proportionally to sockets means from the documentation given below.

|

bunch

|

The

processes are mapped proportionally to sockets and the

processes

are ordered as close as possible on the sockets. |

Below is my environment:

Intel MPI Version:

Intel(R) MPI Library for Linux* OS, Version 2021.6 Build 20220227 (id: 28877f3f32)

output of lscpu:

Architecture: x86_64

CPU op-mode(s): 32-bit, 64-bit

Byte Order: Little Endian

CPU(s): 16

On-line CPU(s) list: 0-15

Thread(s) per core: 1

Core(s) per socket: 8

Socket(s): 2

NUMA node(s): 2

Vendor ID: GenuineIntel

CPU family: 6

Model: 85

Model name: Intel(R) Xeon(R) Bronze 3106 CPU @ 1.70GHz

Stepping: 4

CPU MHz: 1700.000

CPU max MHz: 1700.0000

CPU min MHz: 800.0000

BogoMIPS: 3400.00

Virtualization: VT-x

L1d cache: 32K

L1i cache: 32K

L2 cache: 1024K

L3 cache: 11264K

NUMA node0 CPU(s): 0-7

NUMA node1 CPU(s): 8-15

output of the below command:

I_MPI_DEBUG=5 I_MPI_PIN_PROCESSOR_LIST=:map=bunch mpirun -np 4 -ppn 4 IMB-MPI1 allreduce

[0] MPI startup(): Rank Pid Node name Pin cpu

[0] MPI startup(): 0 18567 skylake1 0

[0] MPI startup(): 1 18568 skylake1 1

[0] MPI startup(): 2 18569 skylake1 8

[0] MPI startup(): 3 18570 skylake1 9

[0] MPI startup(): I_MPI_ROOT=/home/intel/oneapi/mpi/2021.6.0

[0] MPI startup(): I_MPI_MPIRUN=mpirun

[0] MPI startup(): I_MPI_HYDRA_TOPOLIB=hwloc

[0] MPI startup(): I_MPI_PIN_PROCESSOR_LIST=:map=bunch

[0] MPI startup(): I_MPI_INTERNAL_MEM_POLICY=default

[0] MPI startup(): I_MPI_DEBUG=5

As we see in the above output only ranks 0,1 are sitting on the same socket(CPU 0,1) and ranks 2, 4 are on the 2nd socket (CPU 8, 9). But, I wanted to bind all 4 ranks to the same socket. Can someone guide me on how to achieve that?

Thanks in advance.

Regards

Goutham K

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Thanks for posting in the Intel forums.

We are able to reproduce the issue at our end. We are working on it and will get back to you.

Thanks & Regards

Shivani

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello Goutham,

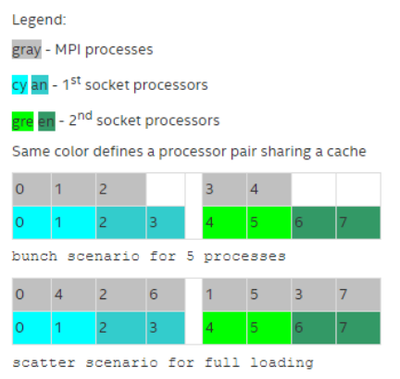

You are experiencing the correct behaviour. There is an example in the complete Intel MPI Reference Guide which you can download here:

https://www.intel.com/content/dam/develop/external/us/en/documents/mpi-devref-linux.pdf

The example is:

For the behaviour you want, please set I_MPI_PIN_PROCESSOR_LIST=0-7 instead.

Cheers,

Rafael

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi @ShivaniK_Intel ,

Thanks for looking into the query.

Hello @Rafael_L_Intel ,

Thanks for the response.

I have a follow-up question - Instead of manually binding I_MPI_PIN_PROCESSOR_LIST=0-7. Is there any environment variable value (like bunch, scatter, spread) using which I can bind all the processes to a single socket?

My use case is - I want to use the same script in different machines and every machine has different physical core locations (Eg: one machine has S1-{0,2,4,6} S2-{1,3,5,7}. So, manually changing every time is a little overhead. So, I wanted to know if I can automate this.

And if possible, Can you explain a bit about how "spread" policy pins processes in Intel MPI for the above-given example?

Thanks in advance.

Regards

Goutham

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Goutham,

What job scheduler are you using? Can you please post the output of "cpuinfo" in the node where the processes are not contiguous?

Cheers!

Rafael

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi @Rafael_L_Intel ,

We are using SLURM.

Requested CPU Information.

Architecture: x86_64

CPU op-mode(s): 32-bit, 64-bit

Byte Order: Little Endian

CPU(s): 76

On-line CPU(s) list: 0-75

Thread(s) per core: 1

Core(s) per socket: 38

Socket(s): 2

NUMA node(s): 2

Vendor ID: GenuineIntel

CPU family: 6

Model: 106

Model name: Intel(R) Xeon(R) Platinum 8368Q CPU @ 2.60GHz

Stepping: 6

CPU MHz: 807.642

CPU max MHz: 3700.0000

CPU min MHz: 800.0000

BogoMIPS: 5200.00

L1d cache: 48K

L1i cache: 32K

L2 cache: 1280K

L3 cache: 58368K

NUMA node0 CPU(s): 0,2,4,6,8,10,12,14,16,18,20,22,24,26,28,30,32,34,36,38,40,42,44,46,48,50,52,54,56,58,60,62,64,66,68,70,72,74

NUMA node1 CPU(s): 1,3,5,7,9,11,13,15,17,19,21,23,25,27,29,31,33,35,37,39,41,43,45,47,49,51,53,55,57,59,61,63,65,67,69,71,73,75

Flags: fpu vme de pse tsc msr pae mce cx8 apic sep mtrr pge mca cmov pat pse36 clflush dts acpi mmx fxsr sse sse2 ss ht tm pbe syscall nx pdpe1gb rdtscp lm constant_tsc art arch_perfmon pebs bts rep_good nopl xtopology nonstop_tsc cpuid aperfmperf pni pclmulqdq dtes64 monitor ds_cpl smx est tm2 ssse3 sdbg fma cx16 xtpr pdcm pcid dca sse4_1 sse4_2 x2apic movbe popcnt tsc_deadline_timer aes xsave avx f16c rdrand lahf_lm abm 3dnowprefetch cpuid_fault epb cat_l3 invpcid_single intel_ppin ssbd mba ibrs ibpb stibp ibrs_enhanced fsgsbase tsc_adjust bmi1 avx2 smep bmi2 erms invpcid cqm rdt_a avx512f avx512dq rdseed adx smap avx512ifma clflushopt clwb intel_pt avx512cd sha_ni avx512bw avx512vl xsaveopt xsavec xgetbv1 xsaves cqm_llc cqm_occup_llc cqm_mbm_total cqm_mbm_local split_lock_detect wbnoinvd dtherm ida arat pln pts avx512vbmi umip pku ospke avx512_vbmi2 gfni vaes vpclmulqdq avx512_vnni avx512_bitalg tme avx512_vpopcntdq la57 rdpid fsrm md_clear pconfig flush_l1d arch_capabilities

Thanks

Goutham

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Goutham,

The output you showed doesn't look much like mine. For instance:

$ which cpuinfo

/opt/intel/oneapi/mpi/2021.6.0//bin/cpuinfo

$ cpuinfo

Intel(R) processor family information utility, Version 2021.6 Build 20220227 (id: 28877f3f32)

Copyright (C) 2005-2022 Intel Corporation. All rights reserved.

===== Processor composition =====

Processor name : Intel(R) Core(TM) i7-8665U

Packages(sockets) : 1

Cores : 4

Processors(CPUs) : 8

Cores per package : 4

Threads per core : 2

===== Processor identification =====

Processor Thread Id. Core Id. Package Id.

0 0 0 0

1 0 1 0

2 0 2 0

3 0 3 0

4 1 0 0

5 1 1 0

6 1 2 0

7 1 3 0

===== Placement on packages =====

Package Id. Core Id. Processors

0 0,1,2,3 (0,4)(1,5)(2,6)(3,7)

===== Cache sharing =====

Cache Size Processors

L1 32 KB (0,4)(1,5)(2,6)(3,7)

L2 256 KB (0,4)(1,5)(2,6)(3,7)

L3 8 MB (0,1,2,3,4,5,6,7)

Did you use cat /proc/cpuinfo instead? In any case, the cores should be sorted by sockets but SLURM (or other job scheduler) may change this pinning. You may disable this reassigning with:

I_MPI_PIN_RESPECT_CPUSET=0

I_MPI_PIN_PROCESSOR_LIST=0-37

If that doesn't work or doesn't sound viable in your case, you can grep the output of the command you just showed, e.g.

I_MPI_PIN_PROCESSOR_LIST=$( <command> | grep -oP "(?<=NUMA node0 CPU).*")

Let me know if that solves the problem,

Rafael

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi @Rafael_L_Intel ,

Thanks for your response and workaround.

I have checked "which cpuinfo" and I can confirm that it is coming from the Intel MPI bin only. I can see similar CPU binding numbers on different machines too. For some machines, the CPUs are numbered continuously but for some machines, CPU's numbered alternatively(not continuously). I also checked "cat /proc/cpuinfo" and it also lists CPUs alternatively. Maybe different CPU families have different numbering? Not sure.

Workarounds I tried:

1) I used I_MPI_PIN_RESPECT_CPUSET=0 and then tried to use the bunch policy but it didn't work.

Command:

I_MPI_PIN_RESPECT_CPUSET=0 I_MPI_DEBUG=5 I_MPI_PIN_PROCESSOR_LIST=:map=bunch mpirun -np 4 -ppn 4 -machinefile hosts IMB-MPI1 allreduce

2) Then I used I_MPI_PIN_RESPECT_CPUSET=0 and I_MPI_PIN_PROCESSOR_LIST=0-55 and IMPI was able to bind all the processes in the given pool only (0-55). But I'm not sure whether the given pool is on 1 socket or on different sockets as we are just forcing IMPI to use cores in the range of 0-55. (There might be the case that CPU 0 and 1 are on different nodes. so this is not what we are looking for)

3) However, manually setting I_MPI_PIN_PROCESSOR_LIST=$( lscpu | grep -oP "(?<=NUMA node0 CPU\(s\): ).*") worked.

Feature Request: I can use the above-mentioned workarounds and make things work on my end. However, I felt it would be nice if there is a variable like a bunch, scatter, spread, etc using which one can use to bind all the processes to a single socket.

Thanks & Regards

Goutham

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello Goutham,

I have forwarded your feature request to the engineering team.

Cheers,

Rafael

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page