- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi everybody

I'm a FPGA hardware beginner

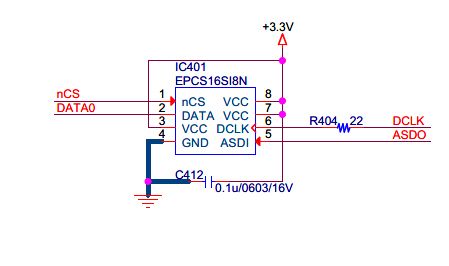

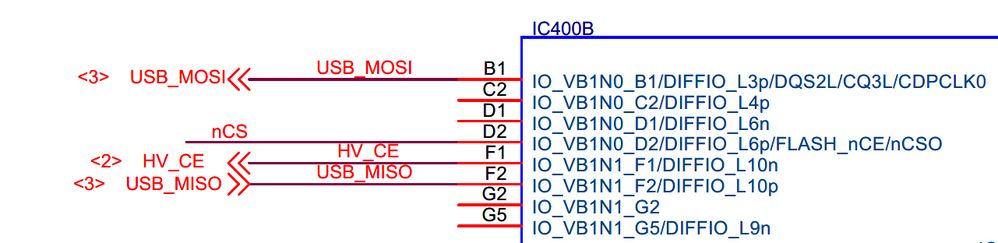

I have a question that I have a EEPROM and fpga

when the power start the EEPROM will write the data to fpga

so I need to using AS mode or JTAG mod or PS mode

I have three data type: sof , pof , jic

component used:

EEPROM :EPCS16

FPGA:EP3C16F256

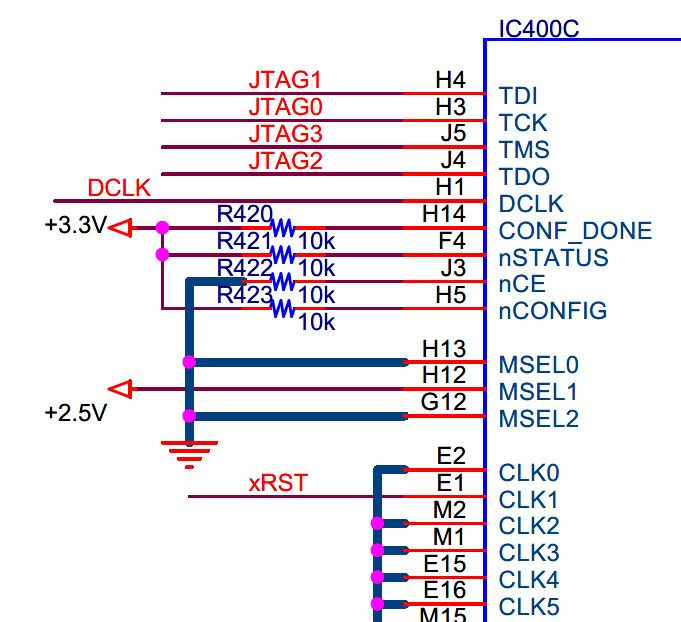

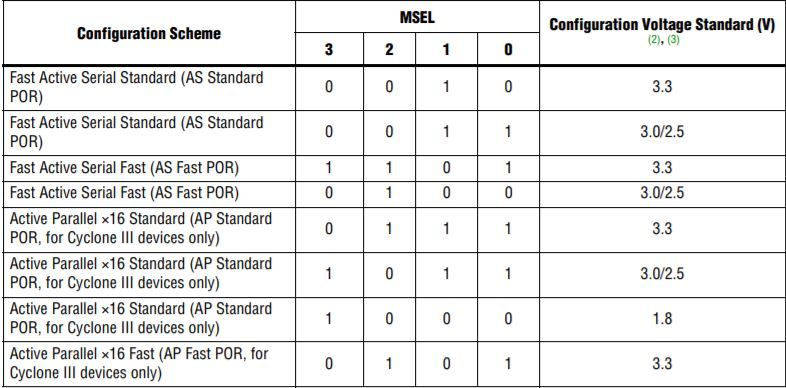

MSEL0:gnd

MSEL1:Vref

MSEL2:gnd

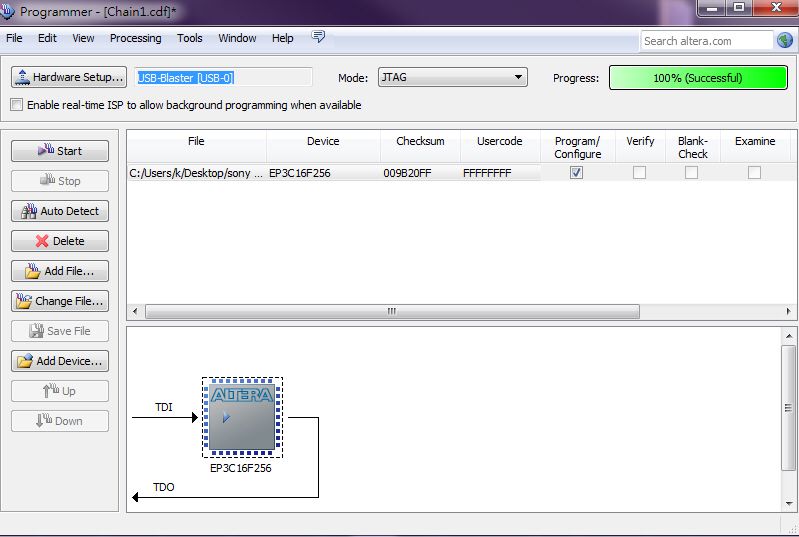

I using usbBlaster and JTAG mode can flash the sof to FPGA but that data is in SRAM when I close off the power the data will disappear.

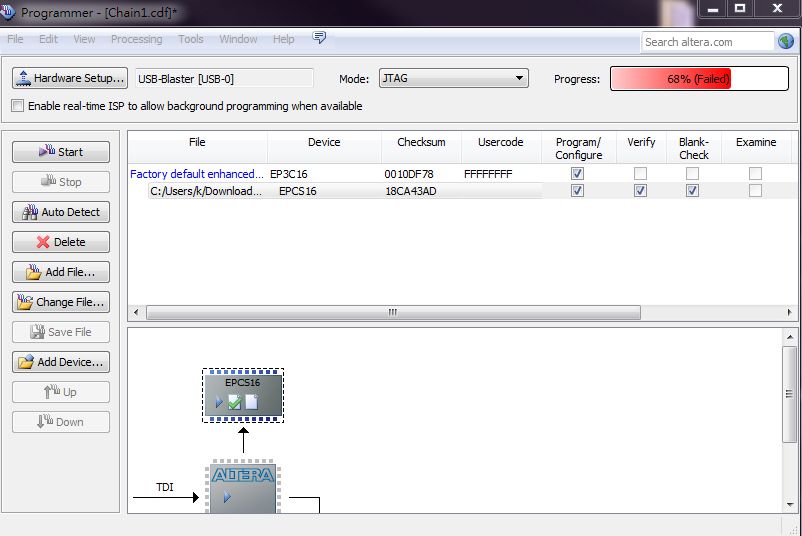

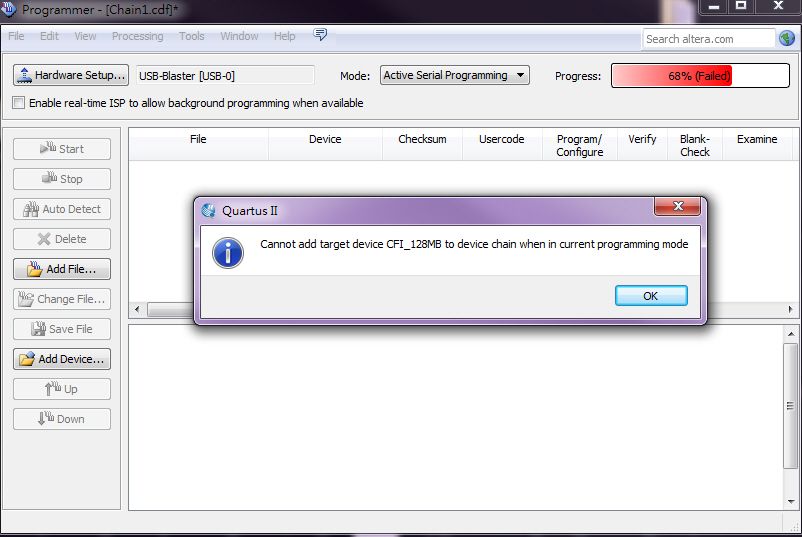

I try to using jic but when I flashing it the error is occurred as shown:

Can't recognize silicon ID for device 1

I try to using pof but I can't add the file on the quartus programming page:

cannot add flash memory programmer object file at the top level

//////////////////////////////////////////////////////////

大家好

想詢問一下FPGA AS mode PS mode JTAG mode的使用方法

好像有個選擇的多工器MSEL[2:0]我現在的接法是

msel0:low

msel1:high

msel2:low

用了三種檔案格式

SOF

POF

JIC

只有SOF成功燒錄,但RESET就消失了

JIC檔案不知道為什麼燒錄到一半都會出現

Can't recognize silicon ID for device 1

POF則是在programming頁面add file時出現(不管MODE是JTAG或Active Serial Programming

cannot add flash memory programmer object file at the top level

- Tags:

- Intel® FPGA Configuration Device EPCS

- Intel® SoC FPGA Embedded Development Suite

- Programmable Devices

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

HI,

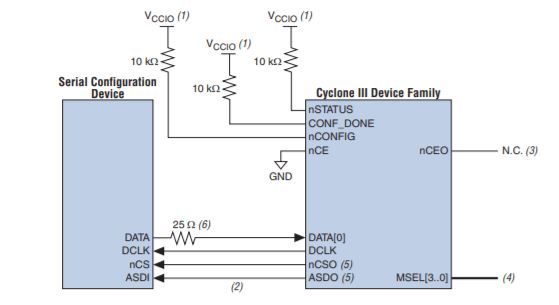

- Have used correct programming headers ? For .jic file, you have to use JTAG header & .pof use AS header. You also may get this error if you have a noisy TCK signal or if the JTAG or AS header are not powered with the correct voltage.

- Have you select correct mode while generating pof? it should be Fast Active Serial Standard ASX1.

Regards

Anand

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

You can also try the following:

Disconnect the pin 6 of the JTAG connector and short nCE of the FPGA to GND without the 10K resistor.

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page