- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

hi

I'm trying to boot a Nios ii processor from EPCQ flash.

I followed the steps described in the following (page 252 and on):

https://www.intel.com/content/dam/www/programmable/us/en/pdfs/literature/hb/nios2/edh_ed_handbook.pdf

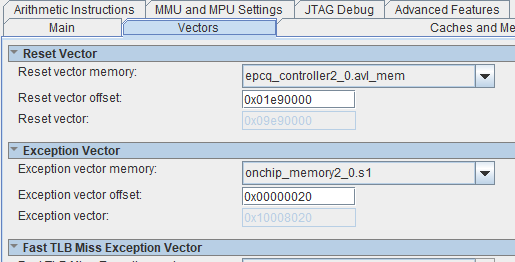

I connected the reset vector to the EPCQ controller and the exception vector to a on chip memory:

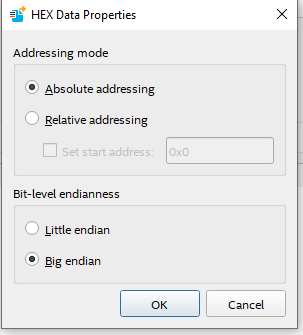

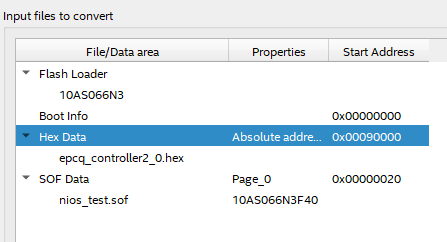

when I try to convert the sof + epcq hex to jic , and use 'absolute addressing':

I get:

why is this the address I'm seeing?

when I choose 'relative path' (and insert the appropriate address) I can convert to JIC but the software does not load from flash (HW does).

I think the issue is not with the software app itself since it does work when loading from JTAG.

any ideas what the issue may be?

thanks!

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

I think you need to review page 261 the following section of the same document you shared:

"

Note: • You may select Relative addressing if you would like to set a relative address to the reset vector offset (0x01E00000) you configured earlier. For example, setting a start address of 0x01F00000 for the relative addressing mode changes the start address to 0x3D00000. • There is an issue for Absolute Addressing for EPCQ. Refer to this knowledge database for more details.

"

plus, please check the available design examples here:

https://fpgacloud.intel.com/devstore/?search=epcq

https://fpgacloud.intel.com/devstore/platform/16.1.0/Standard/board-update-portal-utilizing-epcq-flash-memory-reference-design/

Regards,

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

hi

thanks for the answer.

I tried "relative addressing" inserting manually the address. Any address I give gets a '0x90000' offset (instead of the actual address I inserted in the ip parameter as I would expect from the note you posted).

When using 'relative addressing' , the JIC was generated and downloaded, but the SW does not work.

does the size of the On Chip memory influence this?

Also I noticed that in the reference design you posted the "Active serial clock source" (in: device and pin options -> Configuration) is set to 100M, where in the PDF I posted (page 256) this clock should be 25M.

BR

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi

you should put the exact address mentioned in the vectors of NIOS II.

The clock frequency shouldn't affect the address and booting,I see there is a page called boot info, can you remove it?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

hi

eventually I ended up using the " Nios II Processor Application Copied from EPCQ Flash to RAM Using Boot Copier" option (page 263), that did work.

thanks again.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Great to find the working procedure, do you still need help in the first procedure?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

hi,

no, i'm doing it the other way now (copying EPCQ to RAM).

...but i do have some questions regarding the new method:

- I've found that in order for the SW to upload after power up the nios reset needs to be delayed for some cycles (no sure exactly how many), do you know why this is?

- I'm trying to configure the fpga with EPCQ (as described above) and booting linux with an sd card (when creating the boot file in bsp-editor I checked external_fpga_config box) when using the delay (== counter on top level holding the reset for the nios qsys enabled) the boot gets stuck and the linux does not load , do you know why this may be? can it be connected to the delay i'm implementing?

thanks!

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I have no idea why you put a delay on the NIOS II reset, BTW the main concern is the boot address, you must check the EPCQ flash datasheet to know the sectors inside this flash and know where exactly the correct address you should set to avoid overlay with .sof and give some buffer space to make the boot successful.

Regards,

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page