- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

I am trying to instantiate a DDR LVDS data receiver generated from the IP Catalog for a Max 10 FPGA. i am using the GPIO Lite Intel FPGA IP. The module definition in my system verilog top level design file is as follows:

wds_data_receive_lvds u20

)

.inclock (slvs_clk),

.dout (slvs_2bit_4chan_data_0), // 2bit output

.pad_in (slvs_chan_in_pad[0])

);

The signal "slvs_chan_in_pad[0]" is assigned in the Pin Planner as the positive input to a real lvds buffer. It is part of a 4 bit lvds interface ( input wire [3:0] slvs_chan_in_pad ).

When I try to compile the design, I get the error " 171000 Can't fit design in device" with no explaination of what the problem is.

Can anyone help me learn how to properly assign the lvds input pins to this GPIO Lite Intel FPGA DDR LVDS Receiver IP?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

I have checked the reference that you mentioned in the Max 10 GPIO User's Guide and can not find any way that I am not in compliance with the Specifications of the Max 10 GPIO. This is also substantiated by the fact that the design WORKS if I use the GPIO LVDS Receive Buffers and do the DDR function in logic. It just DOESN'T WORK when I use the GPIO LVDS DDR Receive Buffers.

I am 100% sure that I have assigned the LVDS Device pins correctly and that the pins assigned to these LVDS Signals are actually LVDS Pin Pairs and are correct. If they were incorrect, why would they work in the one case, and not in the other case?????

I am sorry that this is such a difficult problem, but I have recently checked the design's timing and my discrete logic implementation, even though it appears to work in the actual hardware, is not meeting timing constraints. Hence, I need the GPIO DDR Buffers to compile so that I can improve the timing performance.

Thanks for your continuing support,

Bill

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

Can you give us a sample with the same error so we can further investigate?

Thank you.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

Have you resolve your problem? Please let me know. I will have to close this case in 3 days if there is no further response.

Thank you.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Thank you for your response and I am sorry for the late reply. I have attached an archived project that shows the problem. In the "ZTest8_sensor_top.sv" top level design file, I have two different LVDS front ends instantiated and selected by the "ifdef" switch, "USEGPIOLITEDDR" found on line 362. One front end which is instantiated when "USEGPIOLITEDDR" is defined uses the GPIO Lite DDR. The other LVDS front end uses GPIO LVDS receivers and does the DDR function in logic. The second instantiation compiles and works while the first on will not compile and gives the following 4 errors:

Error (15853): Input port I of I/O input buffer "wds_data_receive_lvds2:u203|altera_gpio_lite:wds_data_receive_lvds2_inst|altgpio_one_bit:gpio_one_bit.i_loop[0].altgpio_bit_i|diff_input_buf.diff_input_buf_without_nsleep.ibuf" must be driven by a top-level pin

Error (15853): Input port I of I/O input buffer "wds_data_receive_lvds2:u202|altera_gpio_lite:wds_data_receive_lvds2_inst|altgpio_one_bit:gpio_one_bit.i_loop[0].altgpio_bit_i|diff_input_buf.diff_input_buf_without_nsleep.ibuf" must be driven by a top-level pin

Error (15853): Input port I of I/O input buffer "wds_data_receive_lvds2:u201|altera_gpio_lite:wds_data_receive_lvds2_inst|altgpio_one_bit:gpio_one_bit.i_loop[0].altgpio_bit_i|diff_input_buf.diff_input_buf_without_nsleep.ibuf" must be driven by a top-level pin

Error (15853): Input port I of I/O input buffer "wds_data_receive_lvds2:u200|altera_gpio_lite:wds_data_receive_lvds2_inst|altgpio_one_bit:gpio_one_bit.i_loop[0].altgpio_bit_i|diff_input_buf.diff_input_buf_without_nsleep.ibuf" must be driven by a top-level pin

I am using Quartus 20.1 Lite

Thanks in advance for your assistance with this problem.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

I cannot see errors that you have mentioned in your sample design.

Can I know which device are you using for your design and it's OPN? Have you used Quartus Standard version and see if you still get the same error?

Thank you.

- Tags:

- ors

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I am using a MAX10 device - 10M50DAF484C6GES. I don't have a current license for 20.1 Standard. Hence, I can try to compile the design with it.

Did you compile the design with the "USEGPIOLITEDDR" in both states? If "USEGPIOLITEDDR" is defined it will compile with the GPIO DDR LVDS Receiver instantiated and if "USEGPIOLITEDDR" is commented out it will compile with the same GPIO LVDS Receiver that is used in both conditions to receive the clock signal and the DDR function is accomplished using Verilog logic. "USEGPIOLITEDDR" is found on line 373 of the ZTest8_sensor_top.sv file.

Are you getting no errors with "USEGPIOLITEDDR" in both states?

If you are not seeing the error, then this would indicate that there is some configuration issue with my computer. Would you consider doing a remote debugging session where you dial into my computer so that you can see the error happen on my computer?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

Max 10 series is compatible for both Quartus Standard and Quartus Lite version so this is not happening because of incompatibility of the device. Can you compile your sample design and screenshot me these errors? I have compiled your sample design again and found no errors.

Thank you.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I have compiled the "ZTest8_sensor" and attached a document with the entire compile log showing the errors at the end. I have also included a "screen shot" of Quartus showing the compile errors at the end of the attached document.

Thanks for your continued assistance,

Bill

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

Thank you for your patience. Upon checking on your sample design I found that there are a lot of error that you need to fix first. Some of them are connectivity errors like Error: 13024 Output pins are stuck at Vcc or GND and Error 332182 No Path is Found in Satisfying Assignment.

Please re-check your design on these issues.

- Tags:

- H

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

In the attached archive, I have cleared up all of the 332182 errors and the remaining 13024 errors are part of the design and should not prevent you from finding out why the "GPIO Lite LVDS DDR Input Buffer" will not compile in the design. I have attached both another archive of the project with the error and a document that has all of the messages from Quartus during the failed compile. I am now using Quartus 20.1.1 Lite instead of Quartus 20.1 which I was using previously. This should absolutely be enough information for you to find the problem. If you can't, maybe you can enlist the assistance of someone who can.

Thanks for your assistance in solving this problem,

Bill

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

Upon checking your new sample file I found that have error ' Error (15853): Input port I of I/O input buffer "wds_data_receive_lvds2:u200|altera_gpio_lite:wds_data_receive_lvds2_inst|altgpio_one_bit:gpio_one_bit.i_loop[0].altgpio_bit_i|diff_input_buf.diff_input_buf_without_nsleep.ibuf" must be driven by a top-level pin'. You may get this error because your input buffer is not connected properly in your design. It needed to be connected to a top-level pin. Please check your design and make sure that your I/O input buffer is connected properly to a top-level pin.

Thanks

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

In researching the 15853 Error that you mentioned, I found a logic error in the "ZTest9_Sensor_top.sv" file. Upon correcting the error and compiling the project, it now gets the error -

"Error (171000): Can't fit design in device"

There is no explanation as why it can't fit.

I have attached and new archived project with the logic fix and a document that contains the complete list of messages from the compile. At the bottom of the list of messages is a snap shot of the "Ignored Assignments" Report from the compile.

I hope this helps. Thanks for all of your assistance,

Bill

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

You may get that error because of assigning pin problem. Check your project file or SDC file that has the pin assignments and make you follow the GPIO specs ofthe device. You may get this problem because you assigned pin(s) that is not allowed.

Thank you.

- Tags:

- Hello

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I really believe that the pins are assigned correctly because if I change the switch "USEGPIOLITEDDR" to "Not Defined" and use just the GPIO LVDS Receivers with the same pin assignments and do the DDR function in logic instead of using the GPIO LVDS DDR Receivers to do the DDR function, then it all works OK. By works OK, I mean that it compiles and actually functions properly in the Hardware.

The reason that I am trying to use the GPIO LVDS DDR Receivers instead of just going ahead with my discrete logic implementation is that I feel that the GPIO LVDS DDR Receivers will be a faster and more reliable solution over temperature than the discrete logic implementation that I have.

The question remains why won't my implementation of the GPIO LVDS DDR Receiver work when my GPIO LVDS Receiver with discrete DDR Logic implementation using the same pinouts works?????

Thanks for your continuing support,

Bill

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello Bill,

I understand your frustration. I believe you get this error because your design does not meet the specification of Max 10 GPIO. Please compare your design with Max 10 GPIO especially on IP requirement. You can refer to page 6 from https://www.intel.com/content/dam/www/programmable/us/en/pdfs/literature/hb/max-10/ug_m10_gpio.pdf

Thank you,

Amin

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

I have checked the reference that you mentioned in the Max 10 GPIO User's Guide and can not find any way that I am not in compliance with the Specifications of the Max 10 GPIO. This is also substantiated by the fact that the design WORKS if I use the GPIO LVDS Receive Buffers and do the DDR function in logic. It just DOESN'T WORK when I use the GPIO LVDS DDR Receive Buffers.

I am 100% sure that I have assigned the LVDS Device pins correctly and that the pins assigned to these LVDS Signals are actually LVDS Pin Pairs and are correct. If they were incorrect, why would they work in the one case, and not in the other case?????

I am sorry that this is such a difficult problem, but I have recently checked the design's timing and my discrete logic implementation, even though it appears to work in the actual hardware, is not meeting timing constraints. Hence, I need the GPIO DDR Buffers to compile so that I can improve the timing performance.

Thanks for your continuing support,

Bill

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello Bill,

I understand your frustration. I will do my best to assist you.

There are many documents about DDR that you can find from this file: https://www.intel.com/content/dam/www/programmable/us/en/pdfs/literature/hb/max-10/archives/ug-m10-gpio-15.1.pdf . Your design should be working if your design meet all the specifications of your device. May I know what error did you get regarding the error to compile DDR buffer?

Thank you,

Amin.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

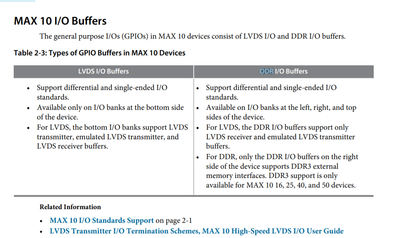

Yes you are right. The pins that I am using are on the bottom of the device and LVDS DDR Buffers are not supported on the bottom of the device. Since the layout for this board is already complete, I will have to live with using the LVDS Receivers and doing the DDR Function with logic.

Thanks for all of your assistance,

Bill

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page