- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

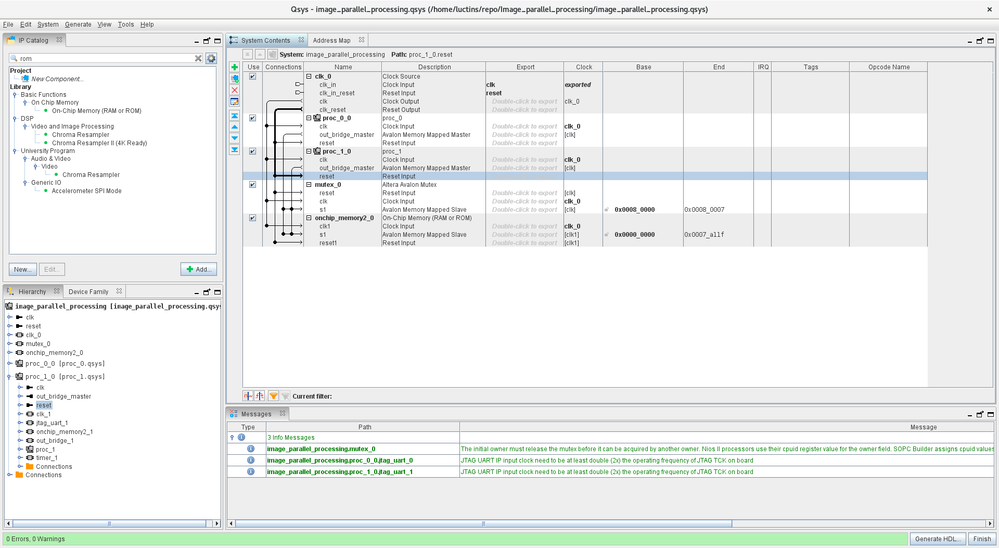

the memory block will be located in the design top level.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

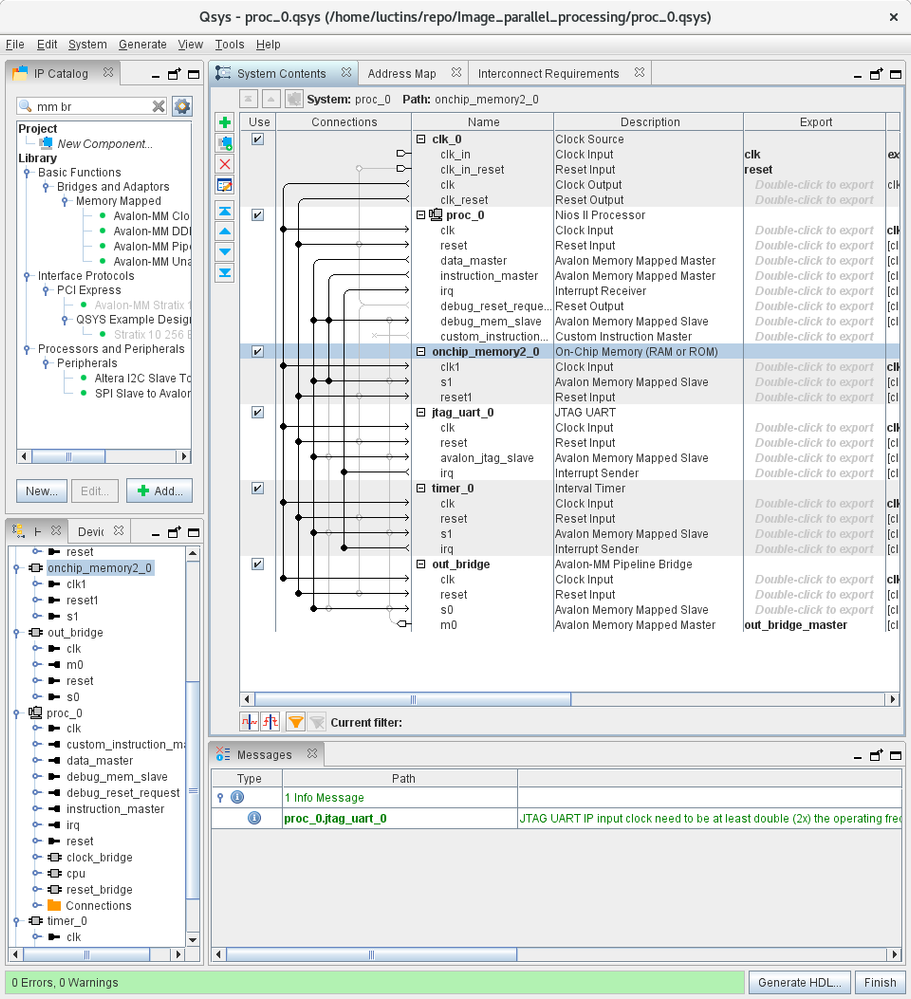

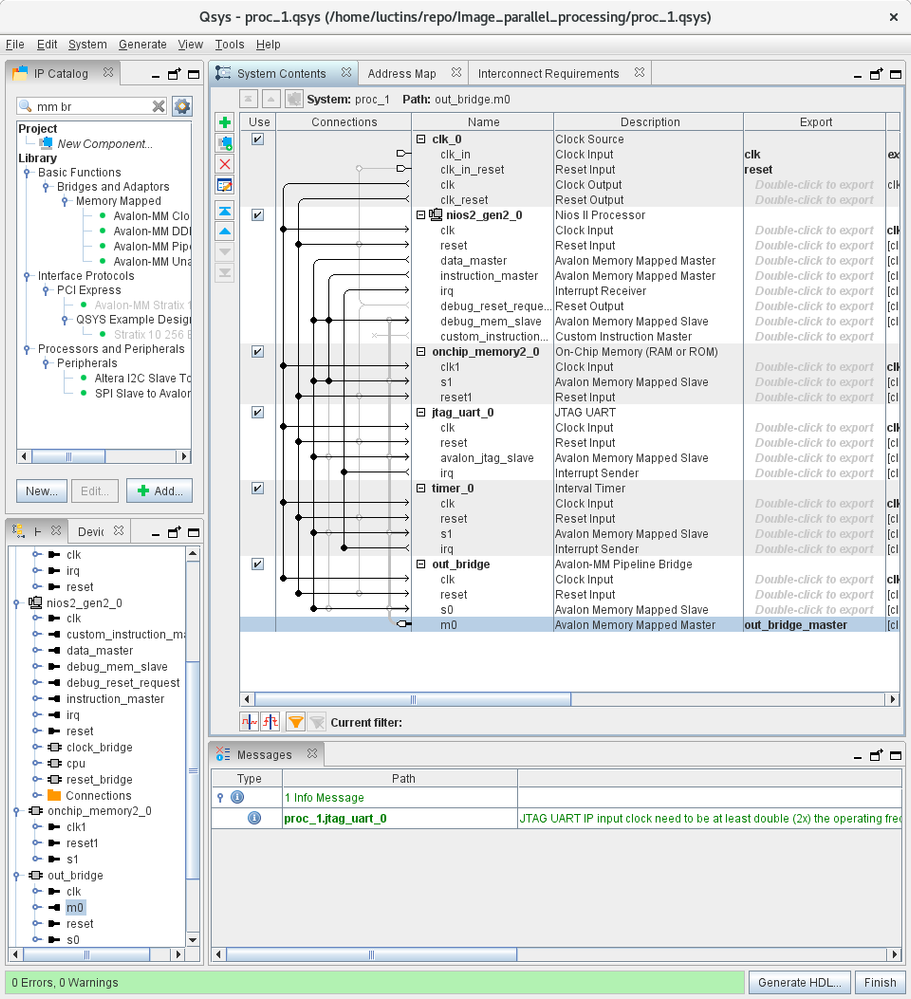

If I understand your question correctly, you would like to have RAM (example) that you can access in your Nios subsystem & in your top level design.

There are multiple ways to do this;

One of them is to create a custom Nios component that contains a dual port RAM.

One side of the RAM can be accessed by your Nios configuration through the Avalon bus.

The other side of the RAM can be exposed by the component via an external component interface.

This interface is the link to your VHDL / Verilog code in your top level design.

Best Regards,

Johi

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page