- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I have an FPGA design on a MAX10 DECA board.

It consists of an outer verilog file with minimal logic mainly pins connecting to a QSYS block, which includes various things including a NIOS II and a custom IP block of my design.

With a couple of the inputs not connected, all works okay. I can program the NIOS II and debug my code.

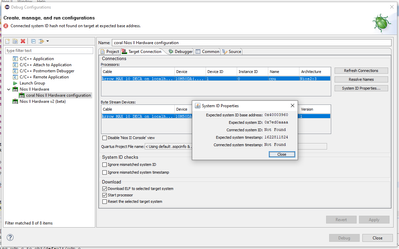

When I connect those inputs, all seems fine until I attempt to run my code. The IDE is unable to read the System ID of the NIOS and so does not download the code. Without the check it simply fails when I attempt to run the code. Except for the fact that it finds the NIOS when I "Refresh Connections", I have no evidence that it is connecting to the NIOS at all.

It is my assumption that without the inputs connected, the bulk of my IP is optimised out. But even with it in it there is not reason, that I can see, why the connection between the IDE and the NIOS should be affected by the presence of the IP.

The IP connects to external pins and an Avalon memory mapped writer with IRQ.

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Did you regenerate your new FPGA bitfile in Quartus and reprogram the new image into your FPGA.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Many, many, many times.

I now have this roughly working, I still have timing warnings that need to be sorted. Some of the code was introducing gross slack issues, removing that allowed programming (some/most of the time).

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page