- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

I'm working on the DE2-115 EVM and I'm trying to operate the SDRAM through NIOS II soft processor ("e" ver). In my code, I fill the memory with the "i" number- while increasing the case address by "i" as well.

I manage to perform full write and read (that now in remark…) operation to the SDRAM for the first about ~144 cycles (Attaché 1). When I'm, trying to fill the memory with more data (running counter "i",let's say 255 cycles), the code is stuck- no printf messages in the UART_JTAG "NIOS II Console" and NIOS II break point at "alt_instruction_exception_entry.c" line 152 (as shown in Attaché 2)

What could possibly be the reason for that kind of error?

See Attaché 3 for more general configuration.

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi IOzan,

Thank you for joining this Intel Community.

May I know what is your SDRAM width?

Let's say if your SDRAM width is 8 bits, then your offset will be +4. If the width is equal to 16 bits, then the offset will be +2.

Also, to perform read/write to memory, using "IOWR/IORD" signal is the best way. I recommend you to use this way and change the offset.

If this doesn't help, please send us the design for debugging purpose

Thanks

Regards,

NAli1

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

I'm sorry but after following the exact tutorial instructions as well as your suggestions (in the previous email), the SDRAM is still only partially working (works well up to first ~144 cycles).

My On my DE2-115 EVM I have two 64MB (128M (32x32)) SDRAMs from the model of IS42S16320B.

I don't really know how to move forward with this problem... L.

I'm attached the complete project for you to have a quick look of the configuration (If you can…).

Thank you very very much…

Idan

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Dear IOzan,

Just to let you know that we are still looking into your issue. I will keep you updated from time to time. Thank you very much for you patience.

Regards,

NAli1

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Dear IOzan,

The exception issue you are facing is normally due to problem with the system that cause Nios break.

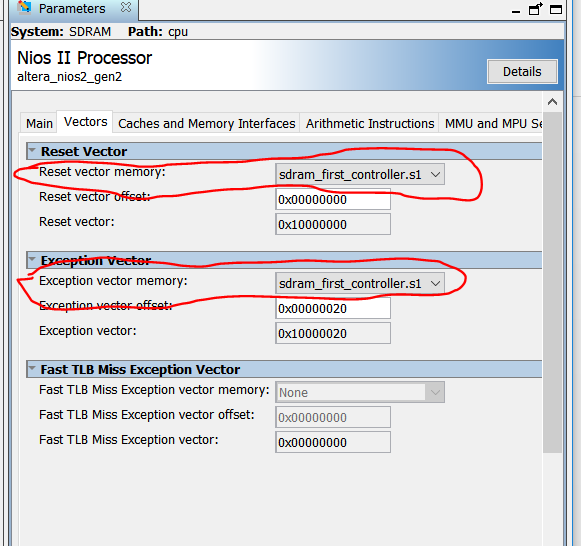

I checked the project you attached. In Qsys perspective, everything looks perfect in term of Nios side and SDRAM side except for the ‘Reset vector memory’ and ‘Exception vector memory’ setting. Can you change this two setting to ‘sdram_first_controller.s1’ and let me know the test results.

If the results is passing then it is OK. If the results is still fail, then I suspect it is due to hardware issue already and you may need to contact the Terasic representative.

Thanks

Regards,

NAli1

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Thank you for your replay but no- it don't work even when changed the vectors (Reset & Exception vector) to point to the SDRAM.

Maybe I can test the hardware from the VHDL section (write and red the entire SDRAM section). Can I do that? Is there any reference of IP code to do that?

Thanks,

Idan

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Please check the available free examples here using SDRAM. These examples are confirmed working and will help you to get your system working.

https://fpgacloud.intel.com/devstore/?search=sdram

Regards

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page