- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi

I’m using the Cyclone V 5CEFA5U19I7 to do my job,but something wrong happened

My work is Receiving differential data and Send in CameraLink format. When I do the Schematic design,I put the differential input and output signals in 5A and 5B Bank, and I use two PLL for the ALTLVDS_RX and ALTLVDS_TX ip core with external pll mode.everything is OK, The correct image is output.However,when I add the DDR3 controller in the Qsys,there are Compile problems as following:

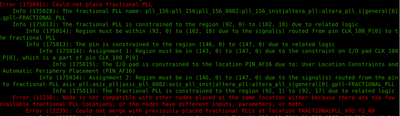

Error (175020): Illegal constraint of fractional PLL to the region (68, 0) to (68, 61): no valid locations in region

Info (175028): The fractional PLL name:

System:inst|Cameralink_mono:cameralink_mono|LVDS_TX:lvds_tx_0|altlvds_tx:ALTLVDS_TX_component|LVDS_TX_lvds_tx1:auto_generated|pll_fclk~FRACTIONAL_PLL

Info (175013): The PLL output counter is constrained to the region (68, 0) to (68, 61) due to related logic

Info (175014): Region must be within (68, 0) to (68, 61) due to the signal(s) routed from the PLL output counter to PLL LVDS output

System:inst|Cameralink_mono:cameralink_mono|LVDS_TX:lvds_tx_0|altlvds_tx:ALTLVDS_TX_component|LVDS_TX_lvds_tx1:auto_generated|pll_ena~PLL_LVDS_OUTPUT

Info (175014): Region must be within (68, 1) to (68, 55) due to the signal(s) routed from the PLL LVDS output to pin cameralink_Data3_p

Info (175015): The I/O pad is constrained to the location PIN_G22 due to: User Location Constraints (PIN_G22)

Error (11238): Node is not compatible with other nodes placed at the same location either because there are too few available fractional PLL locations, or the nodes have different inputs, parameters, or both.

Error (11239): Could not merge with previously placed fractional PLLs at location FRACTIONALPLL_X68_Y54_N0

Info (11237): Already placed at this location: fractional PLL System:inst|Sensor_timing:sensor_timing|Image_rx:image_rx_0|LVDSRX_PLL:lvdsrx_pll_0|LVDSRX_PLL_0002:lvdsrx_pll_inst|altera_pll:altera_pll_i|general[0].gpll~FRACTIONAL_PLL

Info (175013): The fractional PLL is constrained to the region (68, 53) to (68, 61) due to related logic

Info (175034): Assignment 1: Region must be in (0, 13) to (68, 61) due to the signal(s) routed from pin sensor_25m to the fractional PLL

Info (175013): The pin is constrained to the region (40, 61) to (60, 61) due to related logic

Info (175034): Assignment 1: Region must be in (11, 61) to (60, 61) due to the constraint on I/O pad sensor_25m, which is a part of pin sensor_25m

Info (175015): The I/O pad is constrained to the location PIN_G13 due to: User Location Constraints (PIN_G13)

Info (175034): Assignment 2: Region must be in (40, 61) to (60, 61) due to the signal(s) routed from the pin to fractional PLL

System:inst|Sensor_timing:sensor_timing|Image_rx:image_rx_0|LVDSRX_PLL:lvdsrx_pll_0|LVDS

Info (175015): The I/O pad is constrained to the location PIN_G13 due to: User Location Constraints (PIN_G13)

Info (175034): Assignment 2: Region must be in (40, 61) to (60, 61) due to the signal(s) routed from the pin to fractional PLL

System:inst|Sensor_timing:sensor_timing|Image_rx:image_rx_0|LVDSRX_PLL:lvdsrx_pll_0|LVDSRX_PLL_0002:lvdsrx_pll_inst|altera_pll:altera_pll_i|general[0].gpll~FRACTIONAL_PLL

Info (175013): The fractional PLL is constrained to the region (68, 53) to (68, 60) due to related logic

Info (175034): Assignment 2: Region must be in (68, 53) to (68, 60) due to the signal(s) routed from the fractional PLL to PLL output counter

System:inst|Sensor_timing:sensor_timing|Image_rx:image_rx_0|LVDSRX_PLL:lvdsrx_pll_0|LVDSRX_PLL_0002:lvdsrx_pll_inst|altera_pll:altera_pll_i|general[1].gpll~PLL_OUTPUT_COUNTER

Info (175013): The PLL output counter is constrained to the region (68, 53) to (68, 61) due to related logic

Info (175034): Assignment 2: Region must be in (68, 53) to (68, 61) due to the signal(s) routed from the PLL output counter to PLL LVDS output

System:inst|Sensor_timing:sensor_timing|Image_rx:image_rx_0|LVDSRX_PLL:lvdsrx_pll_0|LVDSRX_PLL_0002:lvdsrx_pll_inst|altera_pll:altera_pll_i|general[0].gpll~PLL_LVDS_OUTPUT

Info (175013): The PLL LVDS output is constrained to the region (68, 1) to (68, 55) due to related logic

Info (175014): Region must be within (68, 1) to (68, 55) due to the signal(s) routed from the PLL LVDS output to pin sensor_data_ser_p[6]

Info (175015): The I/O pad is constrained to the location PIN_R16 due to: User Location Constraints (PIN_R16)

Info (175034): Assignment 2: Region must be in (68, 53) to (68, 61) due to the constraint on PLL output counter

System:inst|Sensor_timing:sensor_timing|Image_rx:image_rx_0|LVDSRX_PLL:lvdsrx_pll_0|LVDSRX_PLL_0002:lvdsrx_pll_inst|altera_pll:altera_pll_i|general[0].gpll~PLL_OUTPUT_COUNTER, which is a part of fractional PLL

System:inst|Sensor_timing:sensor_timing|Image_rx:image_rx_0|LVDSRX_PLL:lvdsrx_pll_0|LVDSRX_PLL_0002:lvdsrx_pll_inst|altera_pll:altera_pll_i|general[0].gpll~FRACTIONAL_PLL

Info (175013): The PLL output counter is constrained to the region (68, 53) to (68, 61) due to related logic

Info (175034): Assignment 1: Region must be in (0, 13) to (68, 61) due to the signal(s) routed from fractional PLL

System:inst|Sensor_timing:sensor_timing|Image_rx:image_rx_0|LVDSRX_PLL:lvdsrx_pll_0|LVDSRX_PLL_0002:lvdsrx_pll_inst|altera_pll:altera_pll_i|general[0].gpll~FRACTIONAL_PLL to the PLL output counter

Info (175013): The fractional PLL is constrained to the region (68, 53) to (68, 60) due to related logic

Info (175034): Assignment 1: Region must be in (0, 13) to (68, 60) due to the signal(s) routed from pin sensor_25m to the fractional PLL

…………

I don’t know why, Does DDR3 controller affect my ALTLVDS work? And I try to remove the ALTLVDS_TX module,it Compile OK

I tried many methods finding online. But no one works. Do you had the same or similar question? I need your help! Thank you very much!

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Thank you, I have figured it out.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hey there, I met the similar problem. How did you fix it?

Thanks in advance.

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page