- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

I am trying to derive core numbering within CPUs. I am particularly studying on @McCalpinJohn 's work that he explained here:

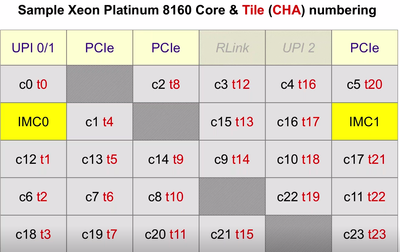

As we can see in his example, core numbering is generally incremented going left to right and then top to bottom, avoiding disabled tiles along its way within the socket. However, note that there is not a well-defined pattern here.

c* is core number, and t* is tile number in the below image.

My question is this:

What if the socket had no disabled tiles? Could we confidently always say that core numbering will be incremented going left to right and then top to bottom? Now that there is no disabled tile to skip over, what is the expected numbering here?

For example, for Skylake XCC socket with 28 cores and no disabled tiles, would the core numbering be:

0 1 2 3 4 5

IMC 6 7 8 9 IMC

10 11 12 13 14 15

16 17 18 19 20 21

22 23 24 25 26 27

Thanks

- Tags:

- Skylake

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

You are in luck! I finally finished my technical report on the numbering of cores and CHA/LLC slices on the SKX/CLX XCC die.

Important background information is in the report Observations on Core Numbering and "Core ID's" in Intel Processors.

The details that you are looking for are in the report Mapping Core and L3 Slice Numbering to Die Locations in Intel Xeon Scalable Processors

- Note that Figure 3 is a bit messed up -- I forgot to add the row of IO blocks across the top and accidentally compensated by adding an extra row of cores across the bottom. The routing of the traffic is otherwise correct. I have a corrected version of the report with a few additional clarifications to the text almost ready to upload, but the version linked above should be good enough.

My report on the mapping of KNL core to CHA numbers is almost complete, but you can also find an independent approach (with identical results) in "Effect of Distributed Directories in Mesh Interconnects"

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

You are in luck! I finally finished my technical report on the numbering of cores and CHA/LLC slices on the SKX/CLX XCC die.

Important background information is in the report Observations on Core Numbering and "Core ID's" in Intel Processors.

The details that you are looking for are in the report Mapping Core and L3 Slice Numbering to Die Locations in Intel Xeon Scalable Processors

- Note that Figure 3 is a bit messed up -- I forgot to add the row of IO blocks across the top and accidentally compensated by adding an extra row of cores across the bottom. The routing of the traffic is otherwise correct. I have a corrected version of the report with a few additional clarifications to the text almost ready to upload, but the version linked above should be good enough.

My report on the mapping of KNL core to CHA numbers is almost complete, but you can also find an independent approach (with identical results) in "Effect of Distributed Directories in Mesh Interconnects"

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page