- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

1SM21BEU2F55E2VG,quartus pro 19.3

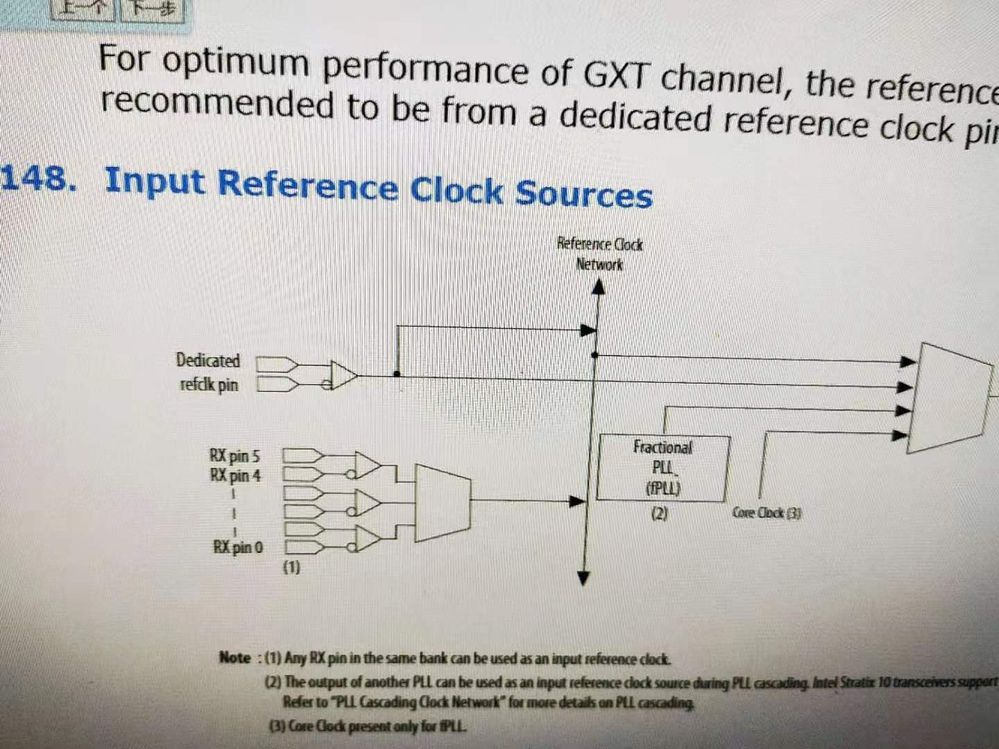

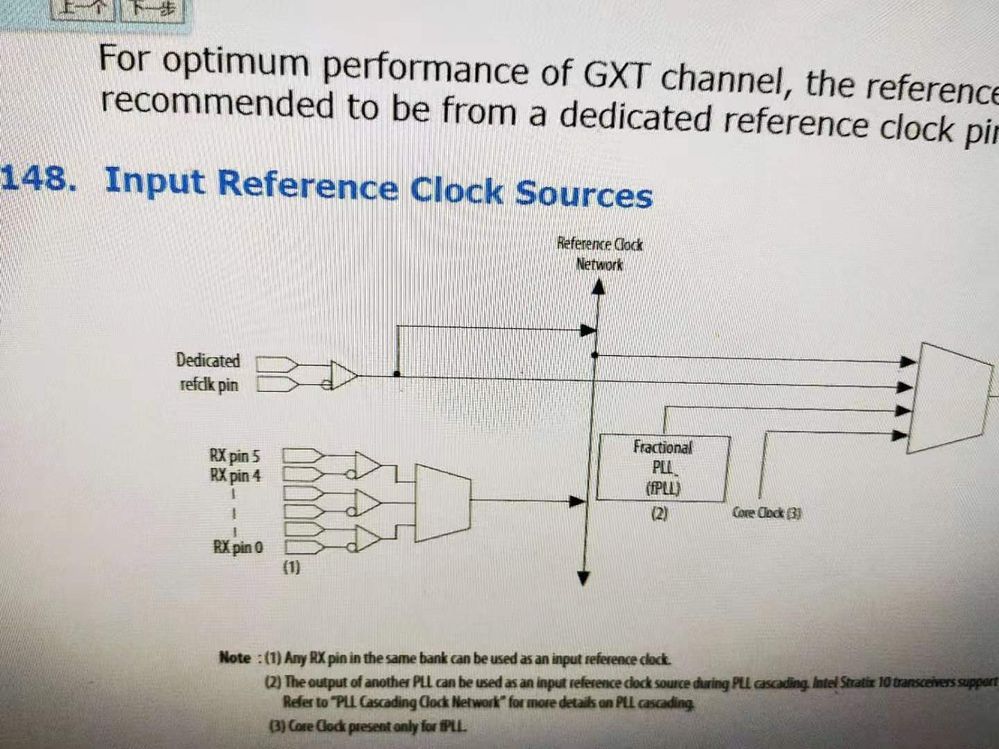

根据收发器的user guide说明,GXT的数据管脚可以作为别的收发器的参考钟

我们的需求是这样,在一个 H tile中,24个收发器,8个输入参考钟

现在8个输入参考钟已经都占用了,还需要额外的4个参考钟,根据手册看到GXT的RX Pin0.. RX Pin 5可以作为输入参考钟,但是我们编译的时候 发现编译无法通过

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

HI,

For a start, below AN778 is a good doc to learn about L-tile/H-tile architecture and pin placement guide.

Now, in order for me to help you debug your issue better, pls share with me your Quartus design QAR file

- So that I can analyze what's the failure error about ? Is it synthesis or fitter error ?

- Also I need to review your transceiver design pin placement and connection as different IP may has its own pin placement restriction guideline

Thanks.

Regards,

dlim

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

HI,

Thanks for sharing customer design and I understand the issue better now.

By right fPLL should be able to accept refclk pin from another Rx pin but customer design will failed fitter compilation unless dedicated refclk pin is used as fPLL refclk pin.

Let me build simple example design to verify fPLL refclk connection then I will get back to you.

Another feedback to your customer is your customer tend to use "generate" function to duplicate transceiver channel count instead of setting the right transceiver channel count in NativePHY IP

- Pls advise your customer not to do it as it's very dangerous.

- It's easily prone to user design connection error and may also mess up NativePHY internal connection generation.

Thanks.

Regards,

dlim

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

HI,

I am able to duplicate the fitter error using simple example design.

Next I want to check is to switch simplex to duplex and also disable GCB clocking to see if it makes a difference.

Thanks.

Regards,

dlim

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

HI,

I have tried with duplex design, reduce data rate and also disable GCB but still failed with fitter error.

I will file an investigation report to Intel Engineering team to look into this issue.

Thanks.

Regards,

Deshi

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

HI,

Sorry, Intel Engineering team respond on this issue is very slow.

I will try my best to continue chase them for update.

Thanks.

Regards,

dlim

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

HI,

Intel Engineering team has confirmed this is IP bug and plan to fix it in next Quartus version which is v20.2 target to be released around early July, 2020.

Thanks.

Regards,

dlim

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Alright, sorry for the delay in respond from Intel Engineering team.

I hope you can feedback to customer accordingly.

For now, I am setting this case to closure.

Thanks.

Regards,

dlim

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page