- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I am using a small 1 port ROM, size 8bits by 64 locations. (Quartus 20.1 Lite)

When I simulate it using ModelSim Altera, providing Clocks and Address, I am only getting Z output.

I have the MIF file in the same directory where the RTL code is.

I am suspecting, as if ModelSim-Altera is not including the MIF file, when running the Sim. How to check and fix this?

What could be possibly wrong?

Thank you,

- Tags:

- MIF

- ROM

- simulation

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Is it true, that the Lite version won't support ROM IP, and only the Licensed version do it?

I never got any warning or error related to that though in Quartus.

What about just running a Sim with ModelSim Altera, using the files which Quartus generated for the ROM and the MIF file.

Thank you

- Tags:

- is

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Tried with a 'Standard' version and a licensed ModelSim-Altera version. Same results.

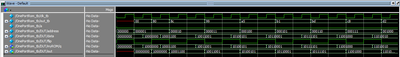

Showing picture below. Bottom three traces are from the ROM instance.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

From the KDB below, it seems that Modelsim tool does not support the memory initialization file (.mif) format and requires you to generate a .hex file. Could you try the solution below and see if it helps?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

We do not receive any response from you to the previous question/reply/answer that I have provided. Please post a response in the next 15 days to allow me to continue to support you. After 15 days, this thread will be transitioned to community support. The community users will be able to help you with your follow-up questions.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

I was able to use the MIF file.

However I used a VHDL model of the ROM, instead of the Verilog, as I could not get it working as mentioned.

The link you provided, is about converting MIF to HEX. And I was still able to use the MIF file.

So the problem is still there, when I use the Verilog model, but not when I switched to the VHDL model of ROM.

I have been using the ModelSim Altera version, which comes with Quartus 20.1 Lite edition.

Thank you,

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Could you help to share a simplified design files with the issue duplicable so I could investigate further?

Please help to provide briefly the steps to reproduce the issue. It helps to duplicate the issue faster.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

I have attached the files. Please let me know of your findings.

(I have renamed the MIF file to TXT extention, as your website doesn't allow to attach it. So please change and save it with MIF extention, on your side.)

- Top file 'OnePortRom.v' - Test Bench 'OnePortRom_tb.v' - Rom model verilog 'RomMem.v' and 'RomMem_bb.v' - Rom model VHDL model 'RomMemVhdl.vhd' - MIF file 'RomInit.mif'

Thank you,

Jaspal

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

Is there an update from your side about this issue?

Were you able to simulate and recreate the problem, on your end?

Thank you

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello Intel Support,

It's been over a month now since I provided the files?

Do you have any update?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Sorry for the delay in response. I forget to re-open the case thus it was closed, till a reply notification come in.

Try to run using the Nativelink feature in the Quartus Lite/Standard.

1. Create a Project with the OnePortRom.v and RomMemVhdl.vhd file

2. Follow the steps 6-8

3. Tools > Run Simulation Tool> RTL simulation

4. Modelsim will auto simulate the result for you.

Initially only clk_tb, out_tb and a signal waveform are shown. You will need to manually add the other signals that you are interest to check.

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page