- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I am porting a design from a 10CX085YF67215G (Cyclone 10 GX, speed grade 5) to a 10AX022C4U19E3LG (Arria 10, speed grade 3). I am using Quartus Prime Pro Edition 21.3.

The design meets timing in the old Cyclone 10, but fails timing (worst setup slack = -0.590) in the more expensive Arria 10.

The timing failures are happening on a group of I/O pins (specifically, output pins). There are only setup timing failures (no hold failures, or anything else).

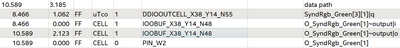

I have compared the timing reports generated by Timing Analyzer (for the same process corner "Slow 900mV 100C Model"). It seems like the Arria 10 is just slower everywhere. For example, the screenshots below show worse timing through the I/O cell to the output pin (there are no routing delays - just delays through the primitive I/O cell).

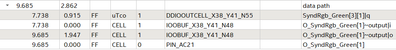

Cyclone 10CX085YF67215G:

Arria 10AX022C4U19E3LG:

Is this expected? One of our reasons for upgrading to Arria 10 (with a better speed grade) was to improve timing performance. Why am I seeing significantly worse timing performance?

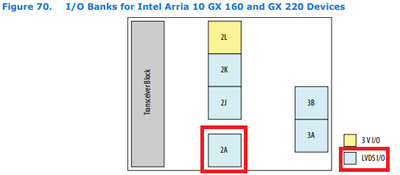

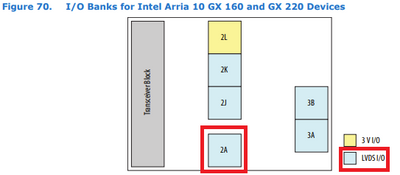

In the Arria 10 device, the pins with the timing failures are mapped to I/O bank 2A, which is an LVDS I/O bank.:

Therefore, my understanding is that this should have decent GPIO timing performance (and certainly not worse than the Cyclone 10 device with speed grade 5).

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

As confirmed by @RichardTanSY_Intel , this is expected behavior. Although it is totally baffling that a more expensive device family, combined with a superior speed grade leads to worse timing performance, I am satisfied that my question has been answered.

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

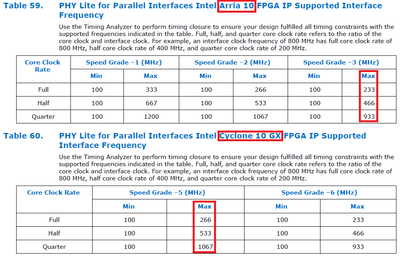

I have found some documentation that seems to confirm that Arria 10 speed grade 3 has worse I/O timing performance than Cyclone 10 GX speed grade 5.

This is from p. 133 of "PHY Lite for Parallel Interfaces Intel® FPGA IP User Guide". I have highlighted the maximum interface frequencies:

It seems like a poor decision to name the speed grades this way. A superior device family (Arria) with a superior speed grade (3) has inferior timing performance to an inferior device family (Cyclone) with an inferior speed grade (5).

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi

May I know does the timing pass if you change to the Arria 10 device with speed grade 1?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

@RichardTanSY_Intel Yes, Arria 10 speed grade 1 meets timing.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I will need to consult our internal team in regards to this IP, could you help to clarify below inquiries:

1. What is the interface frequency of the design?

2. Do you use dynamic reconfiguration in their design?

3. The timing failure is happened in output pins but which is the timing failure path the between IO to FPGA core or external to IO?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

@RichardTanSY_Intel Thank you for your help.

- I need to support a range of frequencies (set at compile time in different FPGA builds), up to 300 MHz. But this is a source-synchronous interface, so the more pressing issue is to meet the setup and hold requirements of the external device.

- No, I do not want to use dynamic reconfiguration.

- The Arria 10 (speed grade 3) appears to be consistently slower than the Cyclone 10 GX (speed grade 5), so timing failures can happen anywhere.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

As mentioned in the user guide, it seems that it is expected when you find the A10 with speed grade 3 is worse than C10 speed grade 5.

Btw, is the timing failed at all corner?

Do you mind to share us the design for further investigate?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

@RichardTanSY_Intel If this is expected behavior, then there would be no sense in addressing your two questions. Wouldn't it just be a waste of time?

Also, my past experience with Intel employees on this forum is that they ask me to provide a project, I spend hours removing sensitive information and uploading the project, then they never bother to look at it. You can easily create your own project. It doesn't seem to matter what is in the project - timing behavior is significantly worse in the more expensive device.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I am sorry to hear that you have a bad experience with the other forum posts in the past but what I can do for you is to provide the support needed in this case.

As these Intel® Cyclone® 10 GX Available Options and A10 Available Options the lowest the number is fastest, and in the PHYlite UG mentioned that,

A10 (Speed grade 2) = C10 (Speed grade 5)

A10 (Speed grade 3)= C10 (Speed grade 6)

Thus, we can't make these comparison apple-to-apple between Arria 10 and Cyclone 10 GX device, and it is also not compatible with speed grade 3 and speed grade 5.

The speed grade 3 of A10 is not the same as speed grade 5 of C10 so it will impact the timing.

The reason I request the design is so that we could check for anything other that the difference in device speed grade.

It is alright if it is not convenience to share your design with us. Perhaps you could provide some insight on below inquiries?

1. Previously you mentioned that in the Arria 10 device, the pins with the timing failures are mapped to I/O bank 2A, which is an LVDS I/O bank.:

May I know the reason you use bank2A instead of other bank?

2. Beside PHYlite IP, does the design contain other IP? How much is the logic utilization of the design?

3. Do you has any SDC file to constrain the timing? Since you are not using dynamic reconfiguration, there will another way to constraint.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

As confirmed by @RichardTanSY_Intel , this is expected behavior. Although it is totally baffling that a more expensive device family, combined with a superior speed grade leads to worse timing performance, I am satisfied that my question has been answered.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Since this thread has been resolve, I will now transition this thread to community support. If you have a new question, feel free to open a new thread to get the support from Intel experts. Otherwise, the community users will continue to help you on this thread. Thank you.

Best Regards,

Richard Tan

p/s: If any answer from the community or Intel support are helpful, please feel free to give Kudos.

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page