- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

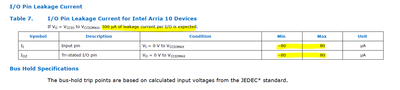

I found Input Leakage spec in Arria10 datasheet Table7.

It shows that Max Ii = 80μA and Min Ii = -80μA.

I understand the spec as following.

If a input pin is pulled-up to 1.8V through 10kΩ, the voltage become 1V at the input pin.

(1.8V - 10KΩ x 80μA)

Is that correct?. If not, please let me know what the spec means.

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

The leakage current number in the datasheet is just a specification (pass/fail) criteria...it doesnt mean that the IO pin itself is leaking that much of current. In fact, IO characteristic differ from pin to pin, device to device. For more accurate, it is advisable to run IO simulation e.g. IBIS.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I No more need to make changes pull-up and pull-down by your answer.

Thank you so much.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Ok but how can we design? We as engineers usually use worst case values when we design. We can not change BOM from products to procuts. And to be honest, these leakage values shown in the datasheet are so high for a leakage parameter. Are you sure no mistakes in the values?

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page