- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi there

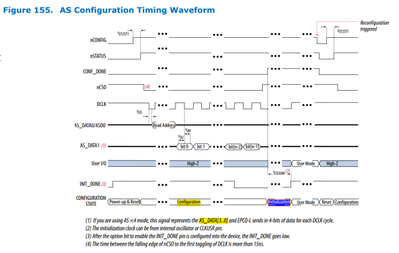

We use 4 pcs 10AX057 in one board, one chip met AS configuration failure occasionally when powered up. Now I doubt the power up sequence maybe out of spec.

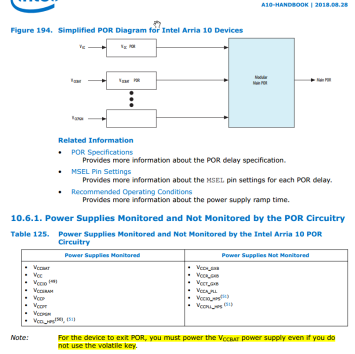

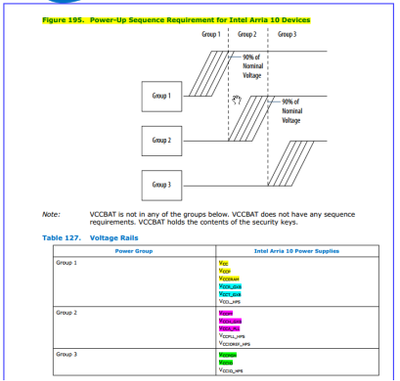

(1)Would like to ask what is the POR trip voltage levels for all the powers that monitered by POR circuit? Is it 90% of nominal voltage?

I will need to measure the POR delay time, which is the time interval between the last VCCIO trip level and nSTATUS pin.

In our sustem, VCC=VCCP=VCCERAM =0.95V, VCCPT=VCCPGM=VCCBAT=VCCIO=1.8V.

I measured nCSO pin (Micron MT25 series flash chip) begin to toggle low repeatedly when the VCCPGM_1.8V power ramps to about 1.2V, I think this is incorrect.

(2) this troubleshooter link seems not working: (https://www.intel.com/content/www/us/en/support/programmable/support-resources/configuration/troubleshooting.html#), if you click the 8th item "

", it still stay in this webpage. pls help check. Thanks.

Thanks a lot.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

(1)Would like to ask what is the POR trip voltage levels for all the powers that monitered by POR circuit? Is it 90% of nominal voltage?

YES.

(2) Meanwhile for item number 2, thanks for the feedback. Will inform internal team on that.

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

up

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

up

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

(1)Would like to ask what is the POR trip voltage levels for all the powers that monitered by POR circuit? Is it 90% of nominal voltage?

YES.

(2) Meanwhile for item number 2, thanks for the feedback. Will inform internal team on that.

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page