- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

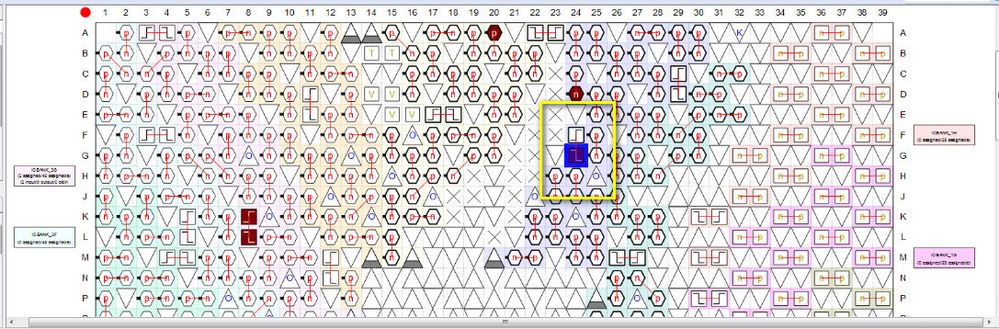

I'm using an Arria 10 and trying to assign my top level ports, according to my schematic, the uart_tx and uart_rx pins are connected to the FPGA through the PIN_G24 and PIN_D24 but when checking in the wire bond view of the pin planner, I found that there is a pin assigned as clock source and I thought that this is the reason that I'm getting a clock conflict and nothing is working on borad after this assignment.

I'm asking if there is an option on pin planner that could ignore the optionnal function of this pin which is a clock source.

thank you

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

What part number are you using? Is this an SoC device? Are you sure you have the correct pin numbers? When you hover your cursor over these pins in the Pin Planner, does the tooltip indicate that an alternate function of these pins is UART? It's strange that a dedicated clock pin would have this function (and it seems incorrect).

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Chloe,

From the pin planner it does appear that you've tied your UART signals to pins D24 and G24. If the fitter didn't issue an error about those assignments then I suspect the problem lies elsewhere.

The fact that the pin is capable of being a dedicated clock shouldn't prevent it from functioning as a UART tx/rx pin. So that fact that the pin planner is showing you that it is a clock pin is not an issue, it's just extra information letting you know that if you needed to bring in a clock or control line then that pin would be a good choice (since it would have a direct path onto the dedicated global signal network).

When working in the pin planner you can have the tool run a quick analysis to determine if your assignments are legal by selecting "Processing / Start I/O Assignment Analysis". This should tell you if there are any illegal assignments and save time relative to a full compilation that errors out.

If your design is compiling, then after compilation I would suggest you look in the report file (CNTL-R to open if it's not already open) under "Fitter / Resource Section" and check to see how your pins were handled (signal type, voltage level, etc.) then cross reference with the board-level schematics to make sure those signal types and locations match the hardware.

Another thing to consider is unused pins. They may be unused in your FPGA design but not on the board. Some of those pins may need to be tied high or low to allow the board to function.

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page