- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

I have Arria 10 (10AS066) Evaluation kit and downloaded the TSE example (a10_soc_devkit_tse.tar.gz -https://releases.rocketboards.org/release/2017.10/tse/hw/)

I was able to compile the project, extract and copy the rbf file to SD card, generate uboot and copy it to SD card as well. The TSE example booted properly to Arria 10 (10AS066) Evaluation kit and able to detect the Marvell 88E1111 of EvB. I was able to ping the board as well.

Now I've migrated (i.e. change the device, pin mapping, clocking,etc.) the FPGA project for my custom board which uses Arria 10 (10AS057) with Marvell MVL88E1512. I've done the following:

- I was able to boot in ARM on my custom board rria 10 (10AS057) but was not able to detect the Marvell MVL88E1512 by sending the "mii info" -interrupt the uboot.

- I've extracted from the modified project the rbf file and copy/paste it on SD card.

- I've generated the uboot from hps_isw_handoff folder and "dd command the uboot" to SD card.

- I didn't update the dtb file. It was same as the EvB (socfpga_arria10_socdk_sdmmc.dtb)

On the HW side:

5. I’ve verified the Voltage rails on the PHYIC.-all good.

6. I’ve verified that the PHY IC is out of reset during boot-up-all good.

7. Checked the clocks (i.e. ETH, FPGA, etc.) -all good.

Issue: I was able to complete the Linux boot-up but the ETH PHY was not detected.

Any suggestions?

Thanks,

Allen Rubis

- Tags:

- Define

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Allen Rubis,

In order to better understand the problem, could you please provide the following information?

- Are you using HPS EMAC or soft TSE IP connect to the MCL88E1512 on your custom board?

- Is either HPS EMAC or soft TSE IP interface working on your custom board?

- Are you update the register map via MDIO as per MVL88E1512 datasheet? This is difference with the Marvel 88E1111 ( What A10 SOC board is using).

- If you are using soft TSE IP, some basic transceiver debug info is needed, are the following signals asserted? If not, which mean the transceiver link is not up and need to further debug on it.

a. rx_is_lockedtodata

b. rx_ready

c. tx_ready

Regards -SKLIM (Intel)

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Here is the MVL88E1512 datasheet that I can search from the web:

By referring to table 29, to support the SGMII to copper, you need to configure the MODE [2:0] register to 001, this is located at General control register 1. Please contact Marvell to get an official datasheet, and also the detail information of how to configure it as per your design requirement if you haven't done so.

Regards SK Lim (Intel)

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi SKLIM,

To answer your questions:

- Are you using HPS EMAC or soft TSE IP connect to the MCL88E1512 on your custom board? soft TSE IP

- Is either HPS EMAC or soft TSE IP interface working on your custom board? HPS EMAC is not connected on the board. I'm current looking to bring-up soft TSE IP which I have issue on bringing up on the board.

- Are you update the register map via MDIO as per MVL88E1512 datasheet? This is difference with the Marvel 88E1111 ( What A10 SOC board is using). May I know where is the MDIO register map on the TSE example- what folder or file? Does the TSE example uses NIOS?. I haven't done any update on the register map (MDIO

- If you are using soft TSE IP, some basic transceiver debug info is needed, are the following signals asserted? If not, which mean the transceiver link is not up and need to further debug on it.

a. rx_is_lockedtodata

b. rx_ready

c. tx_ready

On the TSE example, the rx_is_lockedtodata, rx_ready, tx_ready are not asserted. May I know where is it asserted on the TSE example.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

May I know where in TSE example project, I can change the MODE [2:0] register to 001?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

How does the TSE example configure the ETH PHY? I cannot find NIOS instantiated and there is no software code on the project.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Allen Rubis,

As per the IEEE standard, the external PHY device is required to configure as per their datasheet via the MDIO interface. From soft TSE IP perspective, to access external PHY device, you have to write the PHY address at mdio_addr 1 register (offset 0x10), and followed by the transactions data at MDIO space 1 (offset 0xA0 to 0XBF). Please refer to the TSE IP user guide below for more detail:

https://www.intel.com/content/dam/www/programmable/us/en/pdfs/literature/ug/ug_ethernet.pdf

The design you are referring to is from rocketboard and that is not using NIOS II, the control port of TSE IP is connected to HPS as you can see. Hence, this is require to go through the HPS design flow to update the driver for difference external PHY. You have to check whether the Marvell 88E1512 has been defined in the driver, if not, you can define the parameter of Marvell 88E1512 in the driver by yourself, or you can refer to the newer version of driver that may already defined by someone else (https://github.com/altera-opensource/u-boot-socfpga).

To determine if the Marvell 88E1512 is defined, after you have generated the uboot, you can check the following files.

Marvell.c file:

/drivers/net/phy/

socfpga_common.c

board/altera/socfpga_arria10

Regards -SK Lim

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi SK Lim,

You mention that on rocketboard example the "control port of TSE IP is connected to HPS". May I know on the code or in the configuration that the TSE IP was connected to HPS.

I want to check my project if it I have the same implementation.

I'm targeting to replicate the approach use in TSE example from rocketboard.

Our software engineer is looking on the updating the driver.

I'm generating u-boot using the Makefile generated by BSP editor. How do you update the driver source? I asked this because the BSP editor outputs a default uboot-socfpga folder after sending the make command on uboot_bsp folder.

Thanks,

Allen Rubis

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi SK Lim,

I've reviewed the schematic of the arria10 dev kit [arria10_10as066n3f40_soc_v15.1.2] a10_soc_devkit_03_31_2016.

See attached file. It shows that MDIO and MDC are connected to FPGA pin AV16 and AV17 which is not HPS as shown on pin mapping[TSE example] as well.

May I know where [configuration or code] of the 'control port of TSE IP is connected to HPS' you mentioned above.

Thanks,

Allen Rubis

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Allen Rubis,

From the platform designer, you can notice the control port of TSE IP is connected to the HPS via pb_lwh2f (Avalon-MM Pipeline Bridge).

Yes, the mac0_fpga_mdio (pin_AV16) is connected to the MDIO port of TSE IP. Which mean, to configure the external PHY, the HPS driver need to write the register of the TSE IP's MDIO space 1 via the control port.

Regards -SK Lim

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Thank you very much on this information!

We made an attempr yesterday to update it but was confused because we are updating the output folder (uboot-socfpga) after compiling uboot; instead from the source file.

Do you have any documentation on how to update the driver of the uboot?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I am also building Linux OS for our custom board which took reference from Arria 10 .

I have designed the uboot_mkpimage.bin file and uploaded it in SD Card by taking reference from below links but I am unable to boot the system

https://rocketboards.org/foswiki/Documentation/A10GSRDGeneratingUBootAndUBootDeviceTree

https://rocketboards.org/foswiki/Documentation/A10GSRDCreatingAndUpdatingTheSDCardLTS

In our custom I did the following changes:

1. Replaced DDR4 memory with DDR3 memory at HPS side.

2. Selected UART1 as debug port and connected both UART0 and UART1 interface to HPS.

3. Connected SDMMC for booting at HPS Dedicated Bank.

For the above changes ,I modified ghrd_10AS066N3F40.qsys design which was downloaded from

https://rocketboards.org/foswiki/Documentation/GSRDTagging#Release_binaries .

In the platform designer tool I removed subsystem.qsys file ,which was causing IP license error.This is used for video processing and not required for our project. After applying all the above changes in qsys file , I modified the top.v file and did pin assignment and generated .sof file and handoff folder.

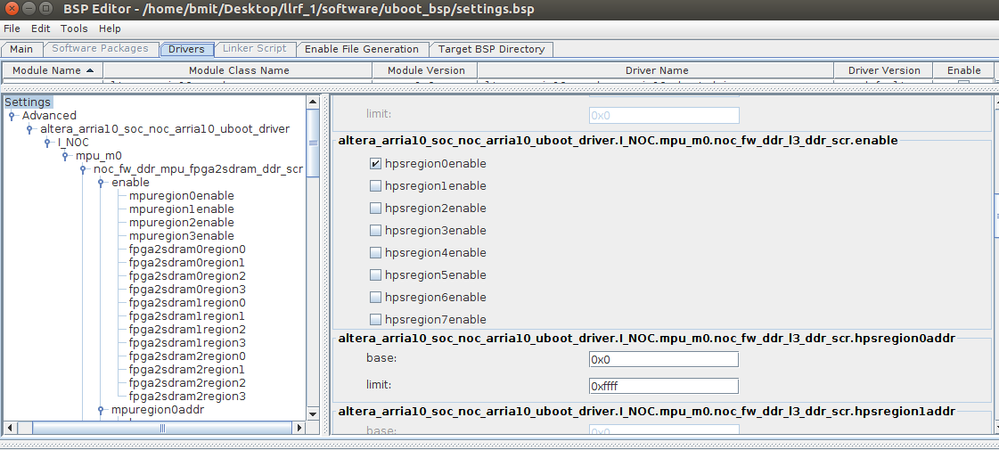

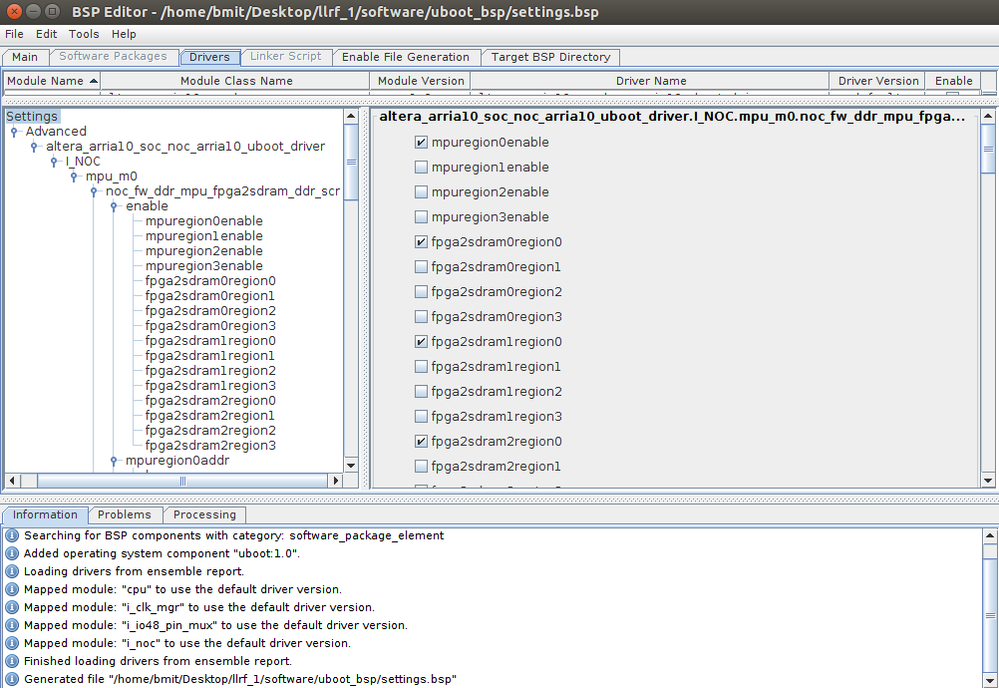

For generating uboot image I am using bsp-editor, but unable to understand the changes which we need to apply in uboot drivers in bsp editor. The attachment contains the bsp-editor image in which modification is required.

For using UART1 as console , we have modified socfpga_arria10.h with following changes-

#define CONFIG_BOOTARGS “console=ttyS1,” __stringify(CONFIG_BAUDRATE)

#define CONFIG_SYS_NS16550_COM1 SOCFPGA_UART1_ADDRESS

Please help with the above query. Also, Are there any further modification we need to do in generated files for above hardware changes?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

You can check this tutorial:

https://rocketboards.org/foswiki/Documentation/PreloaderUbootCustomization131

It shows how to modify the sources of preloader and uboot.

For the PYH support. After the uboot files are generated. You can go to <your project folder>\software\spl_bsp\uboot-socfpga\drivers\net\phy

In phy folder, you can find all th PHY support drivers, referring to the above link, you can apply your customization accordingly.

Thanks

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page