- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Greetings!

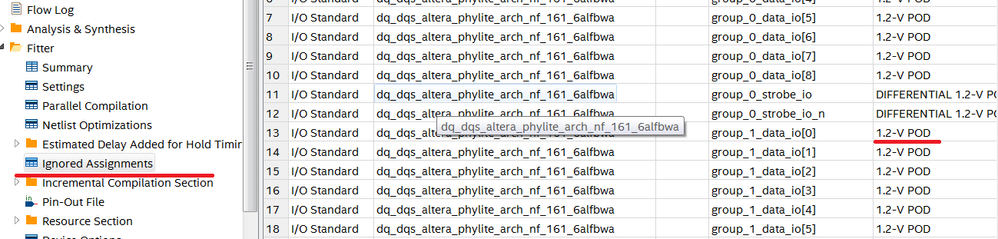

I try to use PhyLite and my own memory controller. So I try to use "1.2-V POD" I/O Standard. But in the Quartus report I can see "Ignored Value" in the "Ignored Assignments" section to my group_0_data_io[*].

The bank voltage is 1.2 V. I/O standard in the QSys is "1.2-V POD" too.

What do I wrong?

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi AKorn9,

Can you provide the full error messages that generated from Quartus and from which stage you seen the error?

Thanks

Regards,

NAli1

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi NAli1_Intel! Thank you for answer!

In fact it is not an error message. I can see it after fitter process finished.

And I can not read data from DDR4. I am using Arria 10 device kit and HiLo daughter card. Unfortunately it is very complicated to connect an oscilloscope to the daughter card and I do not know how memory chip answer to the commands.

To the qsf I added the next strings:

set_instance_assignment -name IO_STANDARD "1.2-V POD" -to DQ[0]

set_instance_assignment -name VREF_MODE VCCIO_70 -to DQ[0]

...and so on.

But it seems the PhyLite does not work as I expect.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I changed 'IO settings' in the 'General' tab in the Qsys from '1.2-V POD' to 'None'. This warning is gone. PHYLite with DDR4 works perfectly.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Dear Akorn9,

I apologize for the delay in response as I were out of office due to holiday. Glad to know that your design is working perfectly now. And thanks for sharing the workaround. Really appreciate it 😊

Feel free to post any update in Intel Forum if you encounter any issue in future.

Thanks and have a nice day !

Regards,

NAli1

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page