- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

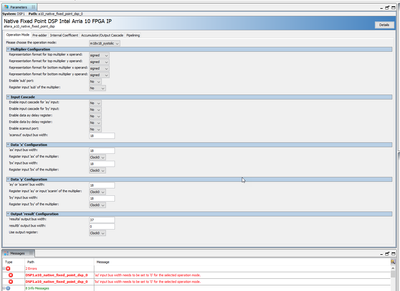

Arria 10 DSP: I am trying to realize

chainout = ( (ay+az)*ax) + ( (by+bz)*bx) + chainin

According to the documentation diagrams and tables, systolic form should support this. But when I set az/bz to 18 in the IP generator it rejects with the reason of 'az' range should be 0 in this form.

Is this a IP generator SW problem, or DSP does not support this setting?

Can I instantiate twentynm_mac_component directly without using the IP generator? Or does Altera have a DSP primitive that I can use to instantiate?

chainout = ( (ay+az)) + ( (by+bz)) + chainin

also works for me. Basically I am trying to pack 5 adders in to one DSP.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Sorry for the delay. I might have overlooked this. Thanks for contacting me. For your information, I have looked into the DSP block architecture in documentation and understand that there should be no issue to implement your target operation.

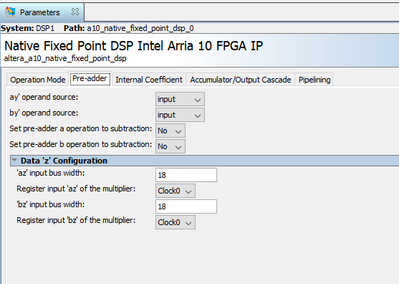

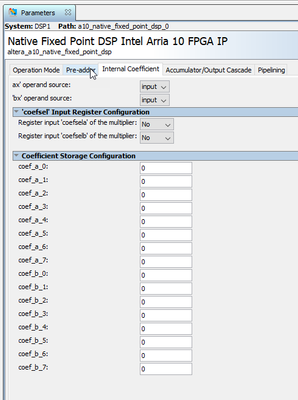

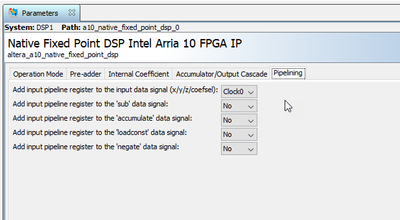

As I tested with the A10 Native Fixed Point DSP IP, I am able to replicate similar error with your configuration. After further debugging, I found that the right option for the ay' and by' operand source should be "preadder" for your target operation. After I switch to "preadder", the error goes away and the IP Block Symbol also looks correct. You can try on your side to see if it works.

Please let me know if there is any concern. Thank you.

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

As I understand it, you have some inquiries related to the A10 DSP IP. To ensure we are on the same page, would you mind to share with me further on the following:

1. What is the specific DSP IP that you are using which trigger error?

2. What is your Quartus version?

3. Mind share with me some screenshot of the IP GUI and the error message that you are seeing?

I would like to perform issue replication on my side to facilitate further debugging.

Please let me know if there is any concern. Thank you.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Altera Std 20.1.1

Native Fixed Point DSP Intel Arria 10 FPGA IP

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Sorry for the delay. I might have overlooked this. Thanks for contacting me. For your information, I have looked into the DSP block architecture in documentation and understand that there should be no issue to implement your target operation.

As I tested with the A10 Native Fixed Point DSP IP, I am able to replicate similar error with your configuration. After further debugging, I found that the right option for the ay' and by' operand source should be "preadder" for your target operation. After I switch to "preadder", the error goes away and the IP Block Symbol also looks correct. You can try on your side to see if it works.

Please let me know if there is any concern. Thank you.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

I believe the initial inquiry has been addressed. This thread will be transitioned to community support. If you have a new question, feel free to open a new thread to get the support from Intel experts. Otherwise, the community users will continue to help you on this thread. Thank you.

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page