- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi, I have Generated example design for emif stratix 10 and simulation scripts too. While simulating in the modelsim ,every signal has default values only. even calib_success&fail both were low only!

one more thing ,I have generated emif core. With Avalon bus signal I am trying to feed some data,in this case aslo calibration is not going high.

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Sir,

I'm Adzim. Thanks for using Intel Community.

May I have a simulation log from the example design that you have run?

Also, can you share the example design with me?

I want to replicate the issue.

Thanks,

Adzim

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I have created example design and generated simulation scripts from Quartus prime pro then simulated through modelsim ,in model sim local_cal_succes is low only.

Basically how much time does simulation takes to complete caliberation (i have used skip caliberation)?

Appolozies! I am not supposed to share any file!

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

can you please share any emif ddr4 stratix design with model sim scripts whcih are working!

Thanks

venkatesh k

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Venkatesh,

I think you have to wait until the simulation is finished because there are some calibration that need to be done before the memory is ready.

If you enable the Abstract PHY mode, the simulation will go faster.

Are you using the msim_setup.tcl script from this directory: <your example design folder>/sim/ed_sim/mentor?

If so than you can run the do file that shared to you to simulate the design.

Thanks,

Adzim

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi sir ,

Thankyou for the reply,

If I do enable Abstract PHY,mem_* signals will not get anything means ,Abstract PHY enables only PHY not Controller! correct?

I Tried with Abstract PHY enable option too, but i didn't get calib_success!

Basically how much time Will take to complete the calibration?

Thanks for run.do file ,but i didn't see any change! still all the signals have default values except pll_clk,usr_clk !

I don't know what the issue is? am not getting output values?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Venkatesh,

I think the time for finishing calibration should be around 30 minutes or more but it's depends on the device that has been used.

Is there any transaction in the log?

I think you need to let the design run -all and finishes the simulation.

It's will give you the result at the end.

Regards,

Adzim

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

YES sir, I did run -all only ,its been more than 2 hours ,still calib_success is low only!

I have been using Stratix 10 EMIF.

in log:

initializing RAM with calibration code ... ed_sim.emif_s10_0.emif_s10_0.arch.arch_inst.io_ssm_inst.io_ssm.inst.<protected> @ 2750 ps

after this empty.

what could be the issue?

Sir,do you have any code for custom data write and read instead of traffic generator?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

one more thing sir,

at the end of compilation ,getting critical warning "DDR4 Timing Requirements not met".

In SDC file, I have created clocks for pll_clk and user_clk!

Is problem is related to timing issues?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

hello sir,

if possible ,could you please share example design and simulation wave form snapshots in modelsim?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Can you share the example design sim scripts and model sim snapshots?

if you are free please Call me +91 8919938367 (india GMT+5:30 ( 9:00 am -6:00 pm)!

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Venkatesh,

I'm not able to share the example design for simulation because the size is exceed the limit.

So I would like you to do these:

- Create new EMIF IP in Parameter Editor.

- Generate example design for EMIF IP in the Parameter Editor.

- Go to this path: <example design project directory>/sim/ed_sim/mentor

- Simulate the msim_setup.tcl with Modelsim.

I can share the EMIF IP setting that I've used to so you can generate the example design with the IP.

The waveform and simulation log also included.

Thanks,

Adzim

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

hi sir,

May I know whwther you have enabled "ABSTRACT PHY " or not?

while restoring the .qar file ,I am getting like this

Error:ERROR: Error(s) found while restoring the archive. See error message(s) for details.

Error: while executing

Error:"project_restore chiptrip.qar"

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Venkatesh,

Yes, I've enabled the Abstract PHY mode in the project.

You need to generate the example design from the EMIF IP in the project.

I've re-attached the project here.

I hope you can extract it without any error.

Maybe the file was corrupted during the compressing process.

Sorry for any trouble.

Regards,

Adzim

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I am getting simulation with Enabling "ABSTRACT PHY" option but I want to enable Hard Controller also in design!in this case simulation i am not getting?

Regards

K venkatesh

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi sir,

If we enable abstract phy option, how can we test this on custom board? Bcz in ABSTRACT PHY mode only PHY enabled not Hard controller?correct?

Regards

K Venkatesh

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi K Venkatesh,

The Abstract PHY mode, Skip Calibration mode and Full Calibration mode are take action on Simulation.

The design has same structure and can be tested on board.

If you want to observe the design in simulation, then you can choose either Skip Calibration or Full Calibration mode.

Regards,

Adzim

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Thankyou so much for clarification!

- local_calib_success is going high ,immediately the controller(amm_ready) is going to busy state(high).

- after some time loca_calib_success going to low ,immediately emif_user_reset_n is going low

if possible ,could you please share Code for instead of Traffic generator for testing DDR4 instead of Traffic generator

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Can you please simulate without Abstract phy and share the result ! as well as design!?

I have tried simulation without enabling abstract phy ! but didn't get any thing!

Thankyou.

K venkatesh

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi K Venkatesh,

How many timeline that your simulation has been running?

I think that the Skip Calibration mode simulation will take a longer time than the Abstract PHY mode.

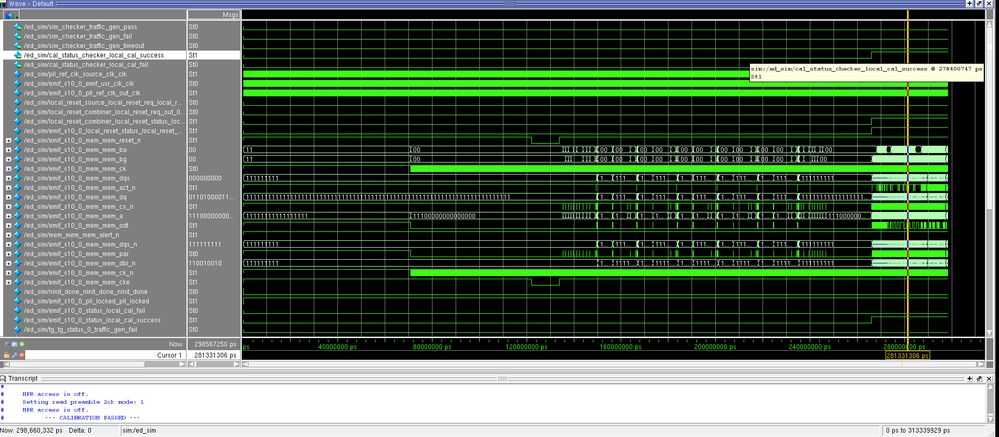

This is the result from my simulation for Skip Calibration mode.

It's taking hours for now and not finish yet.

But it's expected a behavior when simulating with Stratix 10 device.

You can generate the example design from the .qar file that I've shared before but you need to disable the Abstract PHY mode first.

Are you referring to this user guide when implementing the design?

https://www.intel.com/content/dam/www/programmable/us/en/pdfs/literature/ug/ug-20120.pdf

I'm not able to provide the code to replace the Traffic Generator.

Regards,

Adzim

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page