- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I'm using Quartus 16.1

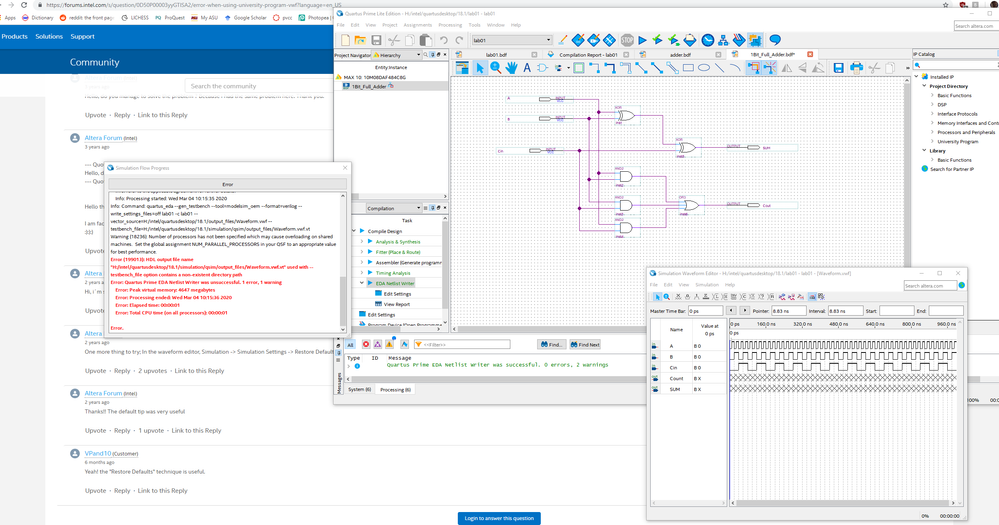

I want to simulate, but when I press Run functional simulation this error occur " Warning (18236): Number of processors has not been specified which may cause overloading on shared machines. Set the global assignment NUM_PARALLEL_PROCESSORS in your QSF to an appropriate value for best performance. Error (199014): Vector source file C:/Users/myusername/Desktop/veri/Waveform1.vwf specified with --testbench_vector_input_file option does not exist Error: Quartus Prime EDA Netlist Writer was unsuccessful. 1 error, 1 warning Error: Peak virtual memory: 471 megabytes Error: Processing ended: Fri Dec 30 22:56:30 2016 Error: Elapsed time: 00:00:01 Error: Total CPU time (on all processors): 00:00:01 Error. "Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

You need to do these five things for Quartus simulation;

1) Tell Quartus to use ModelSim-Altera for the simulation tools (Assignments - EDA Tool Settings - Simulation). 2) Tell Quartus to generate a netlist for functional simulation (Assignments - EDA Tool Settings - Simulation - More EDA Netlist Writer Settings - Generate Functional Simulation Netlist - ON). 3) Tell Quartus to use VHDL for the simulation netlist (Assignments - EDA Tool Settings - Simulation - Format for Output Netlist - VHDL) 4) Tell Quartus where to put the simulation netlist (Assignments - EDA Tool Settings - Simulation - Output Directory). This is usually the "simulation" folder. 5) Tell the simulator (in the simulation waveform editor) to use VHDL for the netlist language (Simulation - Simulation Settings - Use VHDL). Good Luck.- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

I'm total beginner and have exactly same problem as described above. I downloaded Quartus Prime (includes Nios II EDS) (http://dl.altera.com/?edition=lite&platform=windows&version_number=16.1&dlm3_download=1&dlm3_container=dlmcontainer-2&filenames=modelsimsetup-windows.exe__#tabs-2). It installed to C:\intelFPGA_lite\16.1 I created project and then wanted to do some simulation. As described in this document ftp://ftp.altera.com/up/pub/altera_material/16.1/tutorials/vhdl/quartus_ii_simulation.pdf one have to create University Program VWF. When I clicked Run Functional Simulation I got "ModelSim executable not found." error. I downloaded ModelSim-Intel FPGA Edition (includes Starter Edition) (http://dl.altera.com/?edition=lite&platform=windows&version_number=16.1&dlm3_download=1&dlm3_container=dlmcontainer-2&filenames=modelsimsetup-windows.exe__#tabs-2). It installed to C:\intelFPGA\16.1. In Quartus Prime Lite Edition I manually set Tools -> Options -> General -> EDA Tool Options ->ModelSim to C:\intelFPGA\16.1\modelsim_ase\win32aloem (I'm not sure whether the path is right, as I found no tutorial or manual where this is described) In Simulation Waveform Editor I clicked Run Functional Simulation and I got Error (199014) (as described above). I did all settings as described by gj_leeson, but the error persists. Can you please help?- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello, do you manage to solve the problem ? Because i had the same problem here. Thank you.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

--- Quote Start --- Hello, do you manage to solve the problem ? Because i had the same problem here. Thank you. --- Quote End --- Hello there, I am facing exactly the same problem. Can anyone please describe how you have solved the problem ? :):):)

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi, i´m starting with Quartus and find the same problem. The "solution" that i´ve found is not change the name of the .vwf file. When the name is the default one, "waveform.vwf", I have no problem. If I change it, i got trouble.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

One more thing to try; In the waveform editor, Simulation -> Simulation Settings -> Restore Defaults

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Thanks!! The default tip was very useful

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Yeah! the "Restore Defaults" technique is useful.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Default Restore did not work for me. Still getting the same error, even though netlist works before I run waveform.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I also had this problem and it looks like I found an easy workaround:

a) Remove bad wave form file;

b) Clean and rebuild project

c) Create new Waveform.vwf but save it in the project root (not output_files).

d)Press "Generate Modelsim..."

For some reason in my case the vwf file was created in output_files until I forced it to be at the right place. And I also followed the advice to declare path to ModelSim

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

The simulation settings have a chunk of code that tells it where it saves the data to(the .vwf file is just the viewer for the data). In simulation under simulation settings, after you have loaded the nodes and saved your file, click on restore defaults. If you look at the fourth line in the string of code in this menu as you click on Restore Defaults, you will see it change to the name of your file.

onerror {exit -code 1}

vlib work

vlog -work work prob_c5_4.vo

vlog -work work prob_c5_4.vwf.vt

vsim -c -t 1ps -L cyclonev_ver -L altera_ver -L altera_mf_ver -L 220model_ver -L sgate_ver -L altera_lnsim_ver work.prob_c5_4_vlg_vec_tst

vcd file -direction prob_c5_4.msim.vcd

vcd add -internal prob_c5_4_vlg_vec_tst/*

vcd add -internal prob_c5_4_vlg_vec_tst/i1/*

proc simTimestamp {} {

echo "Simulation time: $::now ps"

if { [string equal running [runStatus]] } {

after 2500 simTimestamp

}

}

after 2500 simTimestamp

run -all

quit -f

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page