- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi all ,

My name is İrfan. I am new to Simulink and Altera blocks.

I want to write the systems I use first.

1) Altera cyclone IV E (EP4CE6E22C8N)

2) Matlab R2015a and R2017b

3) Quartus II Web Edition 14.0.0.200 (64-bit)

I am using JTAG communication between fpga and matlab. At the beginning I applied the following respectively.

1) I defined the tool path using the "hdlsetuptoolpath" function. I checked the command line with " !quartus " and no problem.

2) Then, open the "HDL Workflow Advisor" window and select the synthesis tool, as "Altera Quartus II".

3) I chose the target workflow as " FPGA- in-the-Loop ". I wanted to create it myself with the "Create custom board" tab, since there is no fpga in the target platform list.

4) In the "Basic Information" tab, I selected the fpga and clicked "Next" to switch to the "interfaces" tab.

5) Here, I chose "ALTERA JTAG" by clicking "FIL interface". In the "FPGA Input Clock" section, I selected the frequency 50 MHz, 23.pin for "Clock" and 25.pin for "Reset" and clicked "NEXT".

6) I selected the communication format "JTAG" and finished the test phase successfully by clicking "Run Selected Test (s)".

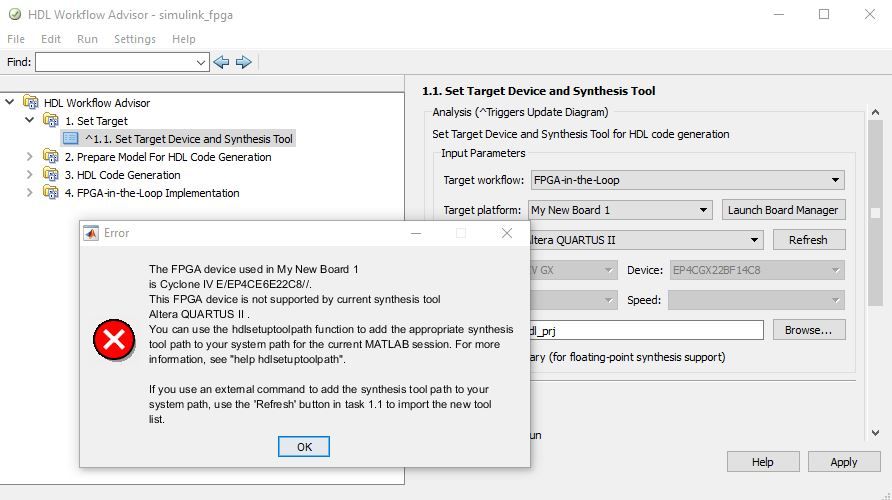

After all these stages, when I started to generate hdl code, I get the error that the Quartus program does not support and cannot synthesize the selected fpga.

Thanks in advance for your help.

Mehmet İrfan Gedik

Error (image)

Not : but I can choose this fpga in the quartus program, so the program supports it

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

and as an extra I would like to ask, can we use blocks other than the library that is opened by "hdllib" in the command line? Other blocks can't be synthesized, right?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Update_1 : I have installed Quartus II 13.0 and now I can choose the appropriate fpga from the list.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

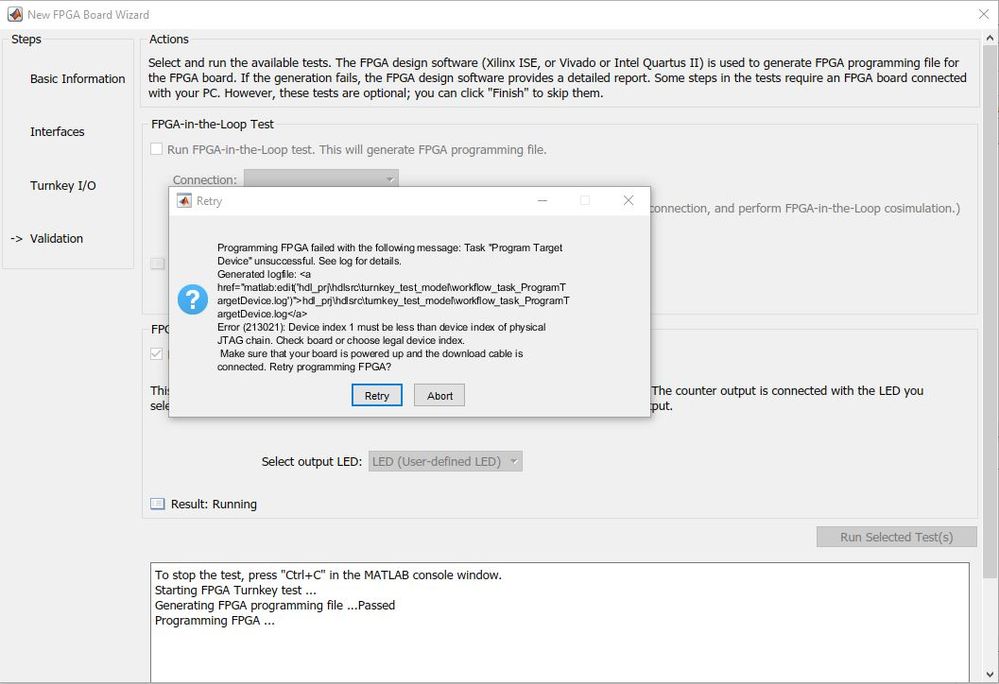

Now there is a different problem. Using the "FPGA Turnkey" I define the led with a 4-bit width in the "Turnkey I / O" tab. However, the error appears. When I compile and synthesize the .sof project file created by Matlab in Quartus, there is no problem.

I need your help on this one,

Error (image)

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Update_2 : I've solved this problem by changing the value of the JTAG chain position.

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page