- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

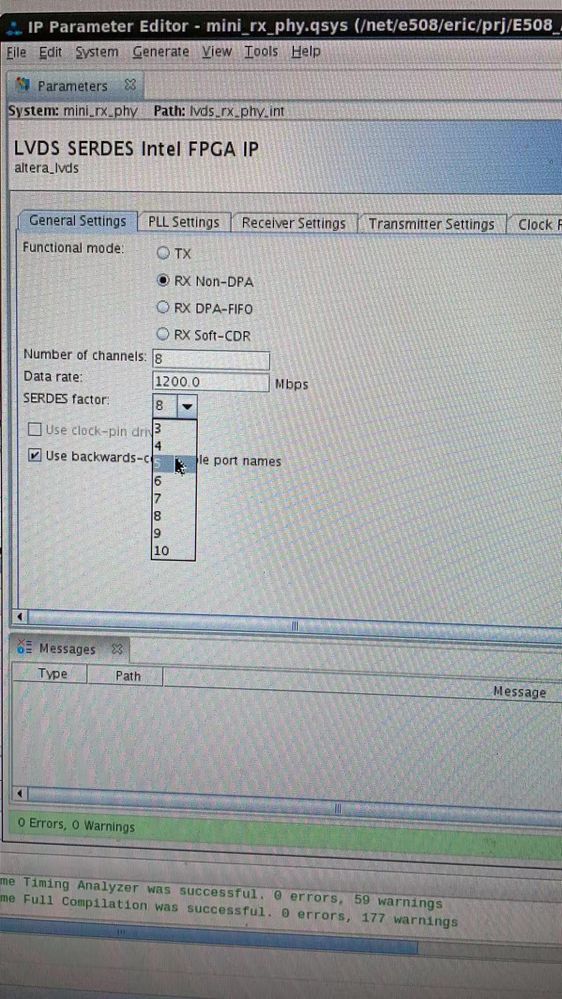

I'm using the LVDS SERDES intel FPGA IP to receive Mini-LVDS signal, I need to receive 2 data by a clock, however, the minimum SERDES factor is 3, so how to set the IP, or anything else I need to set?

Is there a Mini-LVDS example for reference?

Thanks in advance.

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

If you are using x2 factor than you cannot use the LVDS Deserializer as it only support x3-x10. To support SDR and DDR then you will need to use Intel GPIO IP.

Below is the note from the Device LVDS userguide.

The IOE contains two data input registers that can operate in DDR or SDR mode. You can bypass the deserializer to support DDR (x2) and SDR (x1) operations. The deserializer bypass is supported through the GPIO IP core.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi JohnT,

Thanks for your information.

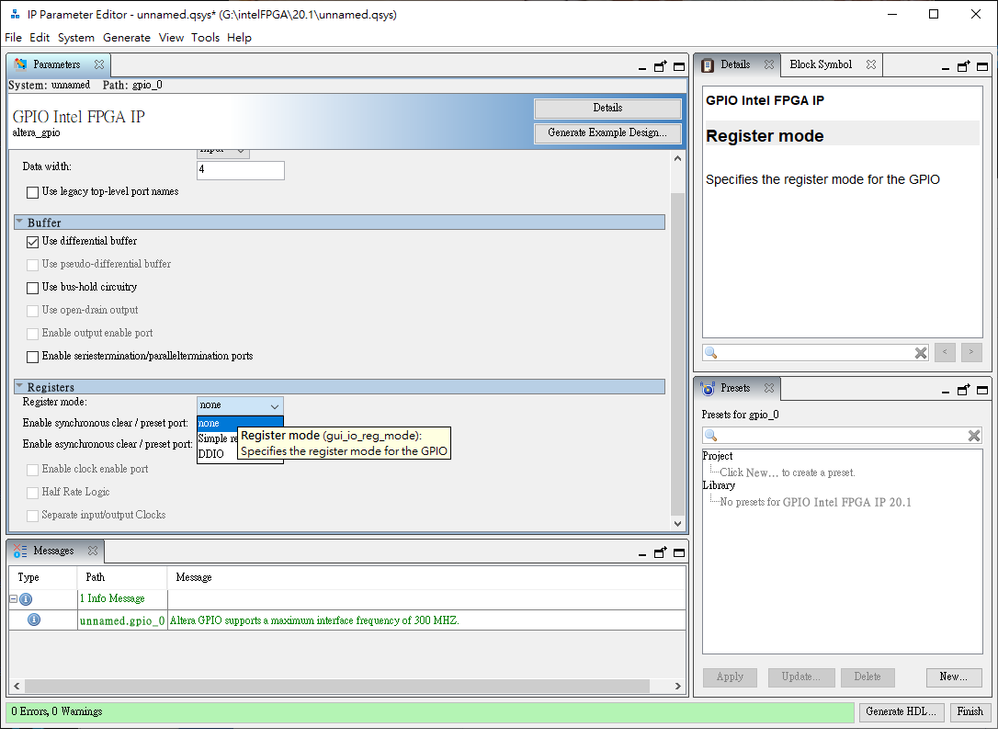

So is it right that I can use the DDIO registers mode in the Intel GPIO IP?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Yes, you are correct.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi JohnT,

Thanks for your fast reply.

Then what's the max speed? How about deal with a 400mhz clock?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

It will depend on the speed grade of the device use and also whether you are able to close the timing in Timing Analyzer

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page