- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

I'm planning to use Intel Stratix 10 GXs inbuilt 10G ethernet HARD IP Phy and interface it to an optical transceiver.

Based on Intel Stratix FPGA document, we can configure single channel of transceiver bank to 28Gbps.

So if i want to use 10G the required connection on schematic level as follows,

1. connect 1 pair of TX & RX(TX_P;TX_N :RX_P;RX_N) directly from transceiver bank to optical transceiver.

2. Provide locally generated 332.5 MHz ref clock for the respective transceiver bank.

Is my understanding correct or am i missing any big picture?

Regards,

AK

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Aravind,

Apologize but I couldn't give a confirmed answer on your query as its out of my expertise. But I would suggest that it will better to re-evaluate the board design again. I guess even though its 0.09V voltage change, it might have some impact.

You may need to discuss with your board designer to determine if it still meet the spec since the datarate also become faster.

Regards,

Pavee

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Aravind,

Based on your description, your understanding is correct on single channel 10G Ethernet.

Below I have attached the single 10G/25G channel blockdiagram for your reference.

Kindly do let me know if it helps.

Regards,

Pavee

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Pavee,

Thank you for your response!

The block diagram is not visible for me, if you share me link for the blk diagram i will look in to it.

One more question regarding - Provide locally generated 332.5 MHz ref clock for the respective transceiver bank in which Ethernet

signals are connected.

whether 332.5Mhz is okay or we need to use 156MHZ or 644.5Mhz!

can you also help me to understand how this frequency value for Ethernet signals are determined or fixed?

Regards,

Aravind

- Tags:

- @Paveetirra_Srie

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Aravind,

Apologize for not be able to see the picture attached in previous reply. I have attached the link below. Kindly refer to page 12 for the Single 10G/25G Channel block diagram.

For reference clock, I would suggest you to use 156MHz or 332.5Mhz. Its depend on your design. Kindly refer to 2.11.17. Clocks page 159-161. It explains more on usage of clocks based on configuration.

Kindly do let me know if it helps.

Regards,

Pavee

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Pavee,

Thanks a lot for your effort!

Actually we are planning to use Intel Stratix 10 FPGA with H-tile(as it supports Ethernet Hard IP) transceiver speed grade -3.

In H-tile Hard IP user guide, in that FPGA with speed grade -1 or -2 only supports 100G or 50G Ethernet(it is obvious than only at least with GX we can get 10Gbps per channel)

My question is as we require only 10G speed, can we go with H-tile with speed grade -3(it can give 17.4 Gbps in Enhanced PCS mode in GX, since speed grade -3 doesn't support GXT).

Kindly confirm whether my understanding is correct & your suggestion.

Regards,

Aravind

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Aravind,

Based on your description, I believe that you're planning to use Intel Stratix 10 FPGA with H-tile. But based on H-tile Ethernet Hard IP User Guide, I don't think transceiver speed grade -3 is supported.

The H-tile Ethernet Hard IP core supports Intel Stratix 10 H-tile devices with these speed grade properties:

• Transceiver speed grade: -1 or -2

The H-Tile Hard IP for Ethernet Intel FPGA IP core supports 50 Gbps and 100 Gbps Ethernet data rate.

My suggestion is why don't you try to use E-Tile Hard IP where it does support 10G Ethernet rate with transceiver speed grade -3.

Kindly have a look E-Tile Hard IP user guide. I believe E-Tile suits your requirement well compared to H-Tile unless you have specific reason to choose H-Tile.

Regards,

Pavee

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Pavee,

Yes, E - Tile Stratix 10 suits our requirement very well.

But we are planning to reuse the schematic design which is already there, that's why we thought of changing only the Tile specification alone.

If we go with H-Tile speed grade -1 or -2, can we use Ethernet Hard IP for 10G speed (with 1 pair of TX and RX ) ?

If it is possible means it will save lot of design time for us!

Kindly provide your valuable suggestion!

Thanks & Regards ,

Aravind

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Aravind,

Thanks for the clarification. If you want to use specifically H-Tile Ethernet Hard IP, then you can't be able to use for your requirement which is 10G as H-tile Ethernet Hard IP only supports 50G and 100G.

Link below explains on Tile and IP core support. Kindly refer to Table 1 - Device and IP Core Support.

Regards,

Pavee

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Pavee,

Thanks for the confirmation!

We planned to use 100G (as it will give room for future improvisation also) along with an optical transceiver which supports 100G.

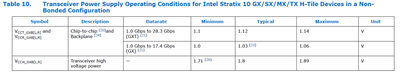

Please refer below table 10 from Intel stratix 10 device datasheet.

In this they have mentioned for speed range 1 to 28.3 Gbps (GXT) typical voltage level for transceiver bank is 1.12V.

Currently we have designed for 1.03V, if i change from 1.03V to 1.12V (roughly 0.09V)

Do we need to do the PDN analysis and re design the FPGA decap section or we can maintain the same, as it is a minor voltage change!

Kindly provide your suggestion!

Regards,

Aravind

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Aravind,

Apologize but I couldn't give a confirmed answer on your query as its out of my expertise. But I would suggest that it will better to re-evaluate the board design again. I guess even though its 0.09V voltage change, it might have some impact.

You may need to discuss with your board designer to determine if it still meet the spec since the datarate also become faster.

Regards,

Pavee

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Pavee,

Thank you for your answers, it helped me a lot!

We are planning to use E-tile itself

Thanks & regards,

Aravind D

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Pavee,

Hope I can get your support once again!

How many I2C and SPI we can use in Intel stratix 10 FPGA, is there any limitation?

If we use one spi(MISO,MOSI,CLK) with 6 chip select pins it will act as single SPI only rite?

Thanks & regards,

Aravind D

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page