- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

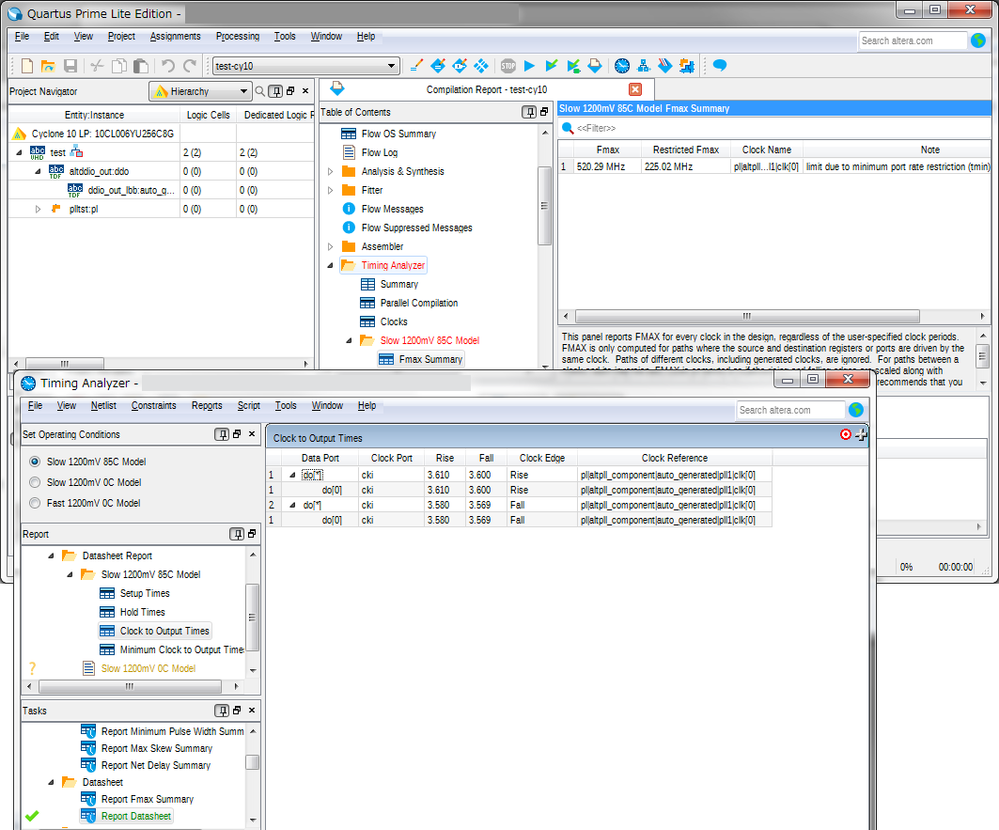

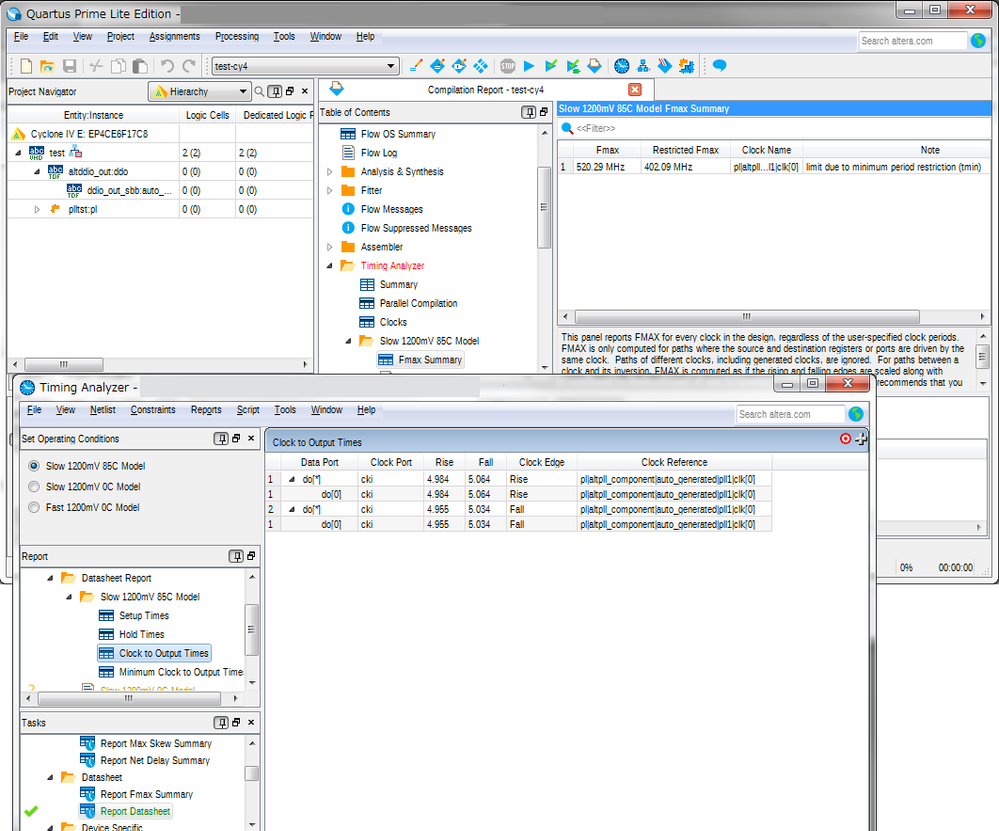

I tested according to the same source code (VHDL) shown below.

The reported delay was almost the same...

but "Cyclone 10 LP" gave the following timing error @300MHz clock.

Is my setting incomplete? or Really "Cyclone 10 LP" slow?

---Timing Analyzer report @Cyclone 10 LP---

DEVICE:10CL006YU256C8G

; Slow 1200mV 85C Model Fmax Summary ;

+------------+-----------------+------------------------------------------------+---------------------------------------------------+

; Fmax ; Restricted Fmax ; Clock Name ; Note ;

+------------+-----------------+------------------------------------------------+---------------------------------------------------+

; 520.29 MHz ; 225.02 MHz ; pl|altpll_component|auto_generated|pll1|clk[0] ; limit due to minimum port rate restriction (tmin) ;

---

; Slow 1200mV 85C Model Minimum Pulse Width Summary ;

+------------------------------------------------+--------+---------------+

; Clock ; Slack ; End Point TNS ;

+------------------------------------------------+--------+---------------+

; pl|altpll_component|auto_generated|pll1|clk[0] ; -1.111 ; -1.111 ;

---Timing Analyzer report @Cyclone IV E---

DEVICE:EP4CE6F17C8

; Slow 1200mV 85C Model Fmax Summary ;

+------------+-----------------+------------------------------------------------+------------------------------------------------+

; Fmax ; Restricted Fmax ; Clock Name ; Note ;

+------------+-----------------+------------------------------------------------+------------------------------------------------+

; 520.29 MHz ; 402.09 MHz ; pl|altpll_component|auto_generated|pll1|clk[0] ; limit due to minimum period restriction (tmin) ;

---

; Slow 1200mV 85C Model Minimum Pulse Width Summary ;

+------------------------------------------------+-------+---------------+

; Clock ; Slack ; End Point TNS ;

+------------------------------------------------+-------+---------------+

; pl|altpll_component|auto_generated|pll1|clk[0] ; 0.846 ; 0.000 ;

---source code (vhdl)---

library ieee;

use ieee.std_logic_1164.all;

library altera_mf;

use altera_mf.altera_mf_components.all;

entity test is

port( rst, cki:in std_logic;

ti:in std_logic_vector(1 to 2);

do:out std_logic_vector(0 to 0));

end;

architecture a of test is

component altddio_out

generic(width:natural;

oe_reg:string:="UNUSED");

port( datain_h, datain_l:in std_logic_vector(width-1 downto 0);

outclock:in std_logic;

oe:in std_logic:='1';

dataout:out std_logic_vector(width-1 downto 0));

end component;

component plltst -- generated by Megawizard plugin manager

port( areset, inclk0:in std_logic:='0';

c0:out std_logic; -- 300MHz

locked:out std_logic);

end component;

signal c0:std_logic;

signal x:std_logic_vector(1 to 2);

begin

pl:plltst port map(rst, cki, c0);

ddo:altddio_out generic map(1)port map(x(1 to 1), x(2 to 2), c0, open, do);

process(c0)begin

if c0'event and c0='1' then

x<=ti;

end if;

end process;

end;

---compiler and other condition---

Quartus Prime Lite Edition 18.1.0.625

no user assignment ... so

I/O standard=2.5V, current strength=8mA, slew rate=2

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

each device had their own speed grade. Each of their own benefits and depends on your needs.

You can refer to https://www.intel.com/content/dam/www/programmable/us/en/pdfs/literature/hb/cyclone-10/c10lp-51002.pdf

https://www.intel.com/content/dam/www/programmable/us/en/pdfs/literature/hb/cyclone-v/cv_51002.pdf

Cyclone E usually is used for Optimized for lowest system cost and power for a wide spectrum of general logic and DSP applications.

Intel® Cyclone® 10 LP FPGAs usually used for optimized for low static power, low-cost applications, such as I/O expansion, sensor fusion, motor/motion control, chip-to-chip bridging, and control.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Thankyou for fast responce ... but,

I made a supplementary test with a FF in an IO pad that is non-DDIO.

so, I found that the speed was virtually the same as shown below.

DEVICE:10CL006YU256C8G (Cyclone 10 LP)

; Slow 1200mV 85C Model Fmax Summary ;

+------------+-----------------+------------------------------------------------+------------------------------------------------+

; Fmax ; Restricted Fmax ; Clock Name ; Note ;

+------------+-----------------+------------------------------------------------+------------------------------------------------+

; 656.17 MHz ; 402.09 MHz ; pl|altpll_component|auto_generated|pll1|clk[0] ; limit due to minimum period restriction (tmin) ;

DEVICE:EP4CE6F17C8 (Cyclone IV E)

; Slow 1200mV 85C Model Fmax Summary ;

+-----------+-----------------+------------------------------------------------+------------------------------------------------+

; Fmax ; Restricted Fmax ; Clock Name ; Note ;

+-----------+-----------------+------------------------------------------------+------------------------------------------------+

; 656.6 MHz ; 402.09 MHz ; pl|altpll_component|auto_generated|pll1|clk[0] ; limit due to minimum period restriction (tmin) ;

From this result, it can be seen that only "Cyclone 10 LP"'s DDIO is about half the speed of non-DDIO,

and "Cyclone IV E"'s DDIO and non-DDIO are almost the same speed.

However, for both devices, the 0.5 cycle time is shorter than the Tco of DDIO output.

Therefore, the shortest pulse may disappear, but a long pulse should provide 0.5 cycle time resolution of the edge.

Is there a problem with my research method?

or Is either wrong?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Can you check does your ddio and non ddio register is inside the IO?

Sometimes, quartus will not automatic put those register to the IO that would cause you to have a slower speed.

If the register is inside the IO, means your analysis is correct.

In arria 10, for speed that more than 200Mhz for DDIO. We would suggest customer to use phylite. But not for Cyclone 10LP.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

https://www.intel.com/content/dam/www/programmable/us/en/pdfs/literature/ug/ug_altera_phylite.pdf

The IP core has a dedicated PHY clock tree in each I/O bank. The PHY clock tree is shorter which yields lower jitter and duty cycle distortion (DCD), enabling designs to achieve higher performance.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

>Can you check does your ddio and non ddio register is inside the IO?

I checked using the resource property editor on both devices.

This time it was necessary to specify "Fast output Register" explicitly on both devices

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Yes, my question is does your result above is base on the register reside inside the I/O?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

ok, My result above is based on a register placed inside an I / O block

and The result of the above placement was examined in the resource property editor

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

If that is the case, then the comparison should be correct. As there are no better timing if those register that you have put inside the IO. Unless you use phylite or altdq_dqs2. Can you try to use AltDDIO to see if the result is different?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I just recall somethings, can you go to timing analyzer and screenshot both delay out for comparison? I remember there are extra delay (like hmc delay stuff) and there is a workaround/avoid on this.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Upload screen capture.

But I'm not sure if it's okay with this screen, so attach the project folder (except db, incremental_db).

The timing report for all cases is in the output_files folder of the attached file.

If there is no workaround, does it mean that cyclon10E can not be used instead of cyclon4E in this situation (like 300MHz x 2 time resolution)?

I'm very curious that cyclon10E's Tco is over 1ns faster under these conditions(2.5V,8mA,slew=2).

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Yes, your analysis is correct. This is also the reason why cyclone 10 E does not have emif to be instantiated. In your case, you will have to use cyclone 10 Gx and use phylite or altdq_dqs for it.

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page