- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

In the FIFO User guide I see the following in Table 7:

Output latency of rdreq to q[] : 1 rdlck.

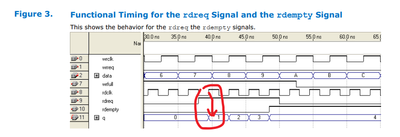

At the same time, on Figure 3 ( Functional Timing for the rdreq Signal and the rdempty Signal

), I see that data on q[] appears on the same rdclk that samples asserted rdreq, i.e. the latency between rdreq and q[] is 0 rdclk (see the screenshot below)

So the question is: what is wrong - the spec value or the timing diagram?

The simulation results with Agilex are consistent with the Figure 3, so perhaps the spec should be corrected?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Andrey,

Thanks for you input. This probably related to documentation spec bug which I will file for fix. Seem there is discrepancy between spec and diagram 3.

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Andrey,

Thanks for you input. This probably related to documentation spec bug which I will file for fix. Seem there is discrepancy between spec and diagram 3.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page