- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi everyone,

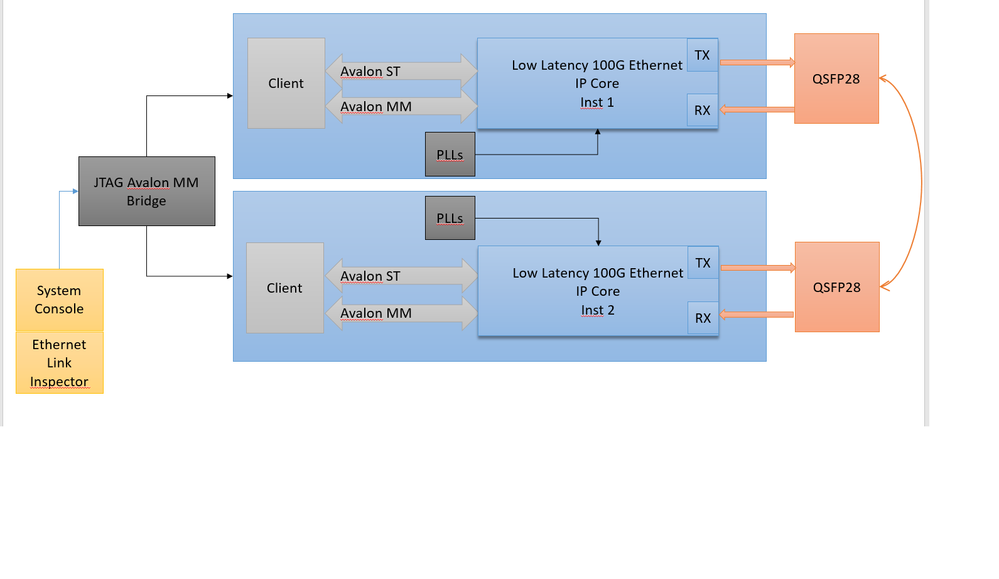

I want to create a loop between 2x Low Latency 100G Ethernet Intel FPGA IP Hardware Design Example on a Stratix 10 MX. The main idea is to implement the entire example design described in alt_e100s10.v twice inside a top level module. The only doubt is given by the avalon jtag master bridge. Can i instantiate two of them, one for each instance? And if not, can i use the Ethernet Link Inspector for the two different instances with only 1 avalon jtag master bridge?

If i was not clear enough, please ask me questions.

Thank you.

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Yes, you can use Avalon Jtag master bridge for more than 1 Ethernet IP, what you need to do is to ensure it has a difference base address.

Regards -SK

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Thanks for your answer.

If i correctly understood i can use two Avalon Jtag master bridges, one for each Ethernet IP, as long as they have a different base address.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

You can use ONE Jtag Master connects to two Ethernet IP with a difference base addresses.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Thank you, i get it now. Can you at last confirm if this architecture is correct?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Yes, it looks fine.

Regards -SK

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Can the addressing be managed by the system console somehow?

Do i need to create a demux to route the data to the right IP or there is any tool in quartus that makes it?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I've noticed this part on the ethernet_link_inspector guide:

3. In the Ethernet Link Inspector - Link Monitor tab, follow these steps to set the

correct JTAG to Avalon Master path:

a. Load the Programming File (*.sof) in System Console by clicking File ➤

Load Design for the detailed JTAG to Avalon Master path.

b. Select List JTAG Masters to see all available JTAG to Avalon Master paths.

c. Select a JTAG to Avalon Master path number from the drop-down box and click

Set JTAG Master.

Note: Each JTAG to Avalon Master path lists two TYPE_NAME (marked by the

blue box in the figure below). The instance name of the JTAG to Avalon

Master path is displayed in one of these TYPE_NAME along with the text

FULL_HPATH (marked by the orange box in the figure below). Select the

JTAG to Avalon Master path number that has the instance name of the

JTAG to Avalon Master path connected to the Ethernet IP.

Seems like they are using multiple jtag masters and then choosing the connected to the IP of interest.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Yes, if using more than one Jtag master, there will have multiple IDs, and you need to select the right one for each instance. To assign the base address, one of the methods is to use avmm master bridge from platform designer (One Jtag Master connect to two AVMM master bridge).

Regards -SK

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Since there are no recent activities, I’ll set this case to close-pending. If you’re still in need of assistance, please reopen this case within the next 20 days.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

i temporarely stopped working on transceivers. Now i'm back on it and i'm trying to figure out the pinout. I downloaded the 1SM21C document by Intel.

I don't understand the relation between the pins and the transceivers. For example, the board i'm using is a BittWare 520N-MX with an Intel Stratix-10 FPGA connected to four QSFP28 ports.

I need to use two of those QSFP28 ports. In particular i need to use the Ethernet 100Gb Hard IP which seems to be usable via port 2 and 3 on the board. So i'm looking forward to the pinout of the port 2 and 3.

The board document says that:

QSFP0_RX[0]p -> pin BB45

QSFP0_RX[0]n -> pin BB44

QSFP0_TX[0]p -> pin BD49

QSFP0_TX[0]n -> pin BD48

and then it says that the rest of the pin mappings follow numerically.

Then i took a look at the Intel document 1SM21C.

I'm a bit confused because in the verilog code RX and TX wires are buses [3:0] so each of them is made of 4 wires.

I don't understand what pin corresponds to each of those wires and also how do i differentiate each QSFP(n) from each other.

For example, i want to use QSFP2 and QSFP3 and i know that each rx and tx wires are composed of 4 wires each. How should i look at the Intel document?

Sorry i'm new to it ...

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi i have another question. I made a wrapper with 2 instances of the IP. It gets synthetized and implemented correctly but it doesn't pass the timing analysis (there is an epic slack, like -90). I don't understand why, i'm looking the paths and it seems like it's something related to the pll that generates the clk100. Have you got any advice please?

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page