- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

I try to use EPE on MAX10. I generate accuTrack_early_pwr.csv file.

My design have some dual port block ram running at 320MHz:

BLOCK,M9K,count,1,ram_mode,"Simple Dual Port",ram_read_during_write,"new",ram_porta_fmax,"80",ram_porta_data_width,"36",ram_porta_addr_width,"2",ram_porta_depth,"4",ram_porta_ena_static_prob,"0.500000",ram_porta_write_ena_static_prob,"0.500000",ram_porta_read_ena_static_prob,"0.000000",avg_ram_porta_output_toggle_ratio,"0.000000",ram_portb_fmax,"320",ram_portb_data_width,"36",ram_portb_addr_width,"2",ram_portb_ena_static_prob,"1.000000",ram_portb_write_ena_static_prob,"0.000000",ram_portb_read_ena_static_prob,"0.500000",avg_ram_portb_output_toggle_ratio,"0.125000"

Import macro generate an error with a limitation at 260MHz :

1 errors encountered!

Line 37: Invalid clock freq on port B!

Cell value must be between 0.0 and 260.0

Skipping!

If in my design a change PLL frequency, import works fine. But I would like to use real frequency : 320MHz.

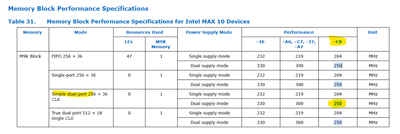

I don't understand where come from this 260MHz limitation. Is it related to this Table 31 of the datasheet?

If yes, there where no warning message about that into Quartus compiling flow.

Thanks for your help and advice.

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hauser,

Let me check this internally and get back to you.

Might take sometime

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Exactly which MAX10 device, speed grade, and temp grade do you have specified in your design?

Because per that table, only the -I6 (fastest) class dual supply device can run the block ram at 320MHz.

You have the -C8 (slowest) highlighted. Is that what you are using?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

I use 10M50DAF484C8G, so C8 grade...so slowest.

But my questions are more, why it there a limitation of 260MHz in EPE rather than 250Mhz?

Why also is there nothing appearing 'in red' as an error if Fmax is violated like setup/hold violations (using 320MHz rather than 250MHz)?

Thanks for your help.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Thiery,

Is it possible for you to attach a small test case for me to replicate it?

I can see there is limitation discrepancy information.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

SyafieqS,

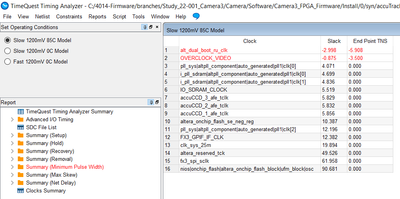

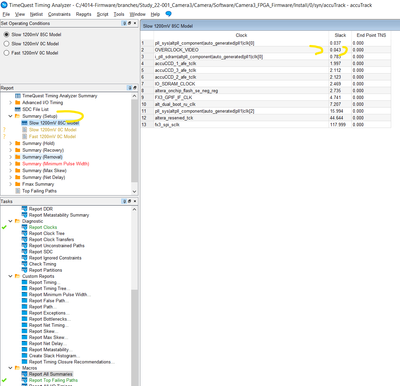

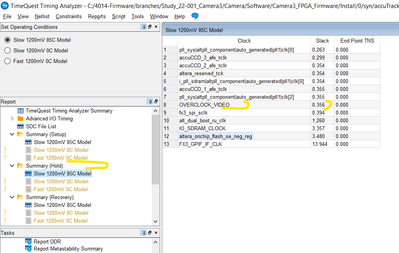

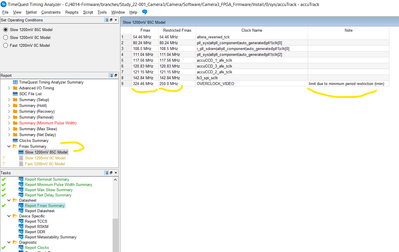

It's not possible for me to send you my project. But I've attached some screenshots of discrepancy informations in TimeQuest :

Report all summaries show a few error on minimum pulse width , but it's ok:

OVERCLOCK_VIDEO have positive slack in setup and hold (so it's ok):

and Fmax summary show a limitation on 'OVERCLOCK_VIDEO', setted at 320MHz using PLL, but with restriction at 250MHz (according the datasheet value):

So my points are :

1°) there is a Fmax violation (320MHz >> 250MHz max allowable frequency), without underline in red. why? Isn't it a timing error?

It doesn't appear in 'report all summaries', neither in 'report top failing path'.

2°) the M9K datasheet limitation is 250MHz. This limitation is increased to 260MHz in Early Power Estimator .xls import macro. Why? is it a typo in EPE?

Thanks for your feedback.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hauser,

Understood,

I am checking this internally for more clarification

Will get to you once there is any findings

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Hauser,

In the meantime, what version of Quartus are you using?

Is it possible for you to run the design in latest Quartus build of your supported device?

We can utilize the new features and bugs/fixes that have be added in the past few years? and see if the issue is persist?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi SyafieqS,

I will take over this subject from my colleague. We work with the version 15.1 of Quartus (I know it's old). We wanted to upgrade to the latest version but unfortunately we have a sdram block in our design and the IP is not present in the version 21.1. I tried with the version 20.1.1 and I have the same type of notification as with the version 15.1...

Thank you in advance for your feedbacks

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi tobiasmil1,

Understood. I will get back to you with update regarding the issue.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

This is taking sometimes as engineering is working on high priority case, I will let you know any update

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

This seem taking longer than we expected.

May I know how urgent this issue is?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

This issue is not a really urgent matter.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Noted. If that's so, since this case has been idling, I would put this to close pending and suggest you to create a new case mentining this case for follow up in future. In the meantime you may change the frequency as documented to avoid any further issue. Let me know any concern on this.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Let me know if there is any update from previous reply

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page