- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Shafiq,

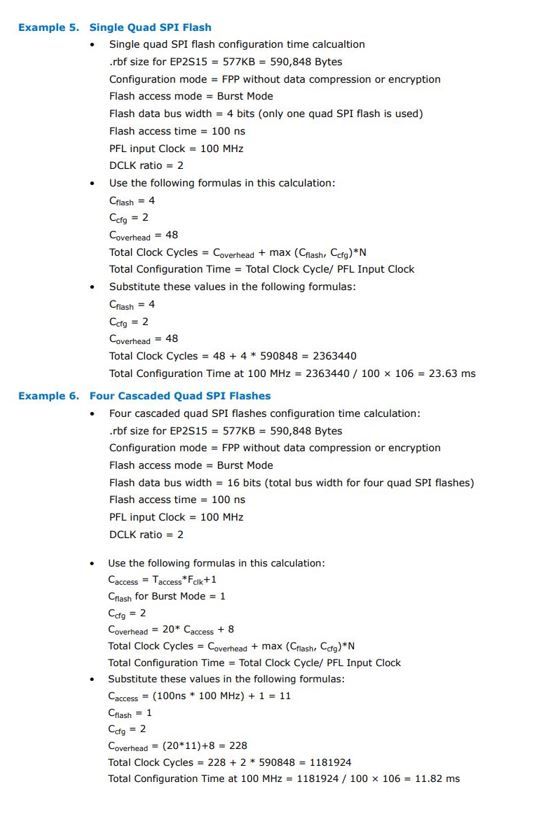

Not entirely clear yet. I understand your point about more data storage. I do not understand why the configuration time example on page 49 states the time calculation is identical to 16-bit CFI flash. Can you please clarify the time calculation example?

thanks.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi CBlow,

I'm a little bit confuse with description. He is asking Configuration Data bus not Flash Data bus. (I'll edit the description to avoid another confusion).

For flash data bus wise, yes it will reduce the configuration time. If one QSPI flash is used, the flash data bus is 4 bits. Whereas, if cascaded four QSPI flash is used, the flash data bus is 16 bits.

Thus for Configuration time, cascaded four QSPI flash have shorter configuration time compare to one QSPI flash.

Cheers

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page