- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

You can set simulation end time,

'Edit'->'Set End Time' from Waveform editor Menu bar.

Please let me know if you have any different concern.

Regards,

Vicky

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

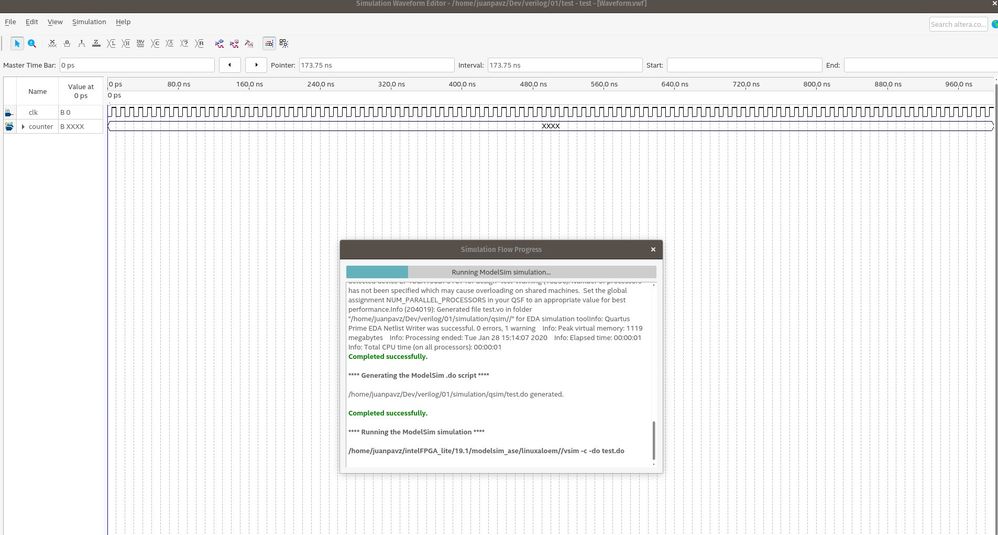

I looked the end time and it shows: 1 uS (I changed with 500nS but nothing happend)

More information:

Simulation options in Functional Simulation Settings: quartus_eda --gen_testbench --tool=modelsim_oem --format=verilog --write_settings_files=off test -c test --vector_source="/home/juanpavz/Dev/verilog/01/Waveform.vwf" --testbench_file="/home/juanpavz/Dev/verilog/01/simulation/qsim/Waveform.vwf.vt"

---------------------------------

when I start linux, I use terminal:

~$ intelFPGA_lite/19.1/quartus/bin/quartus

/home/user/intelFPGA_lite/19.1/quartus/linux64/libstdc++.so.6: version `GLIBCXX_3.4.20' not found (required by /lib/x86_64-linux-gnu/libproxy.so.1)

Failed to load module: /usr/lib/x86_64-linux-gnu/gio/modules/libgiolibproxy.so

I can make analysis and synthesis (ctrl + k), view RTL and compile (ctrl + l). But I can't simulate with University Program VWF

And , when I start the program it shows an error message: Error (14565): Can't connect to the Intel FPGA website to check for updates.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Could you provide the design file using any text file or word file for replication purpose?

Regards,

Vicky

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page