- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

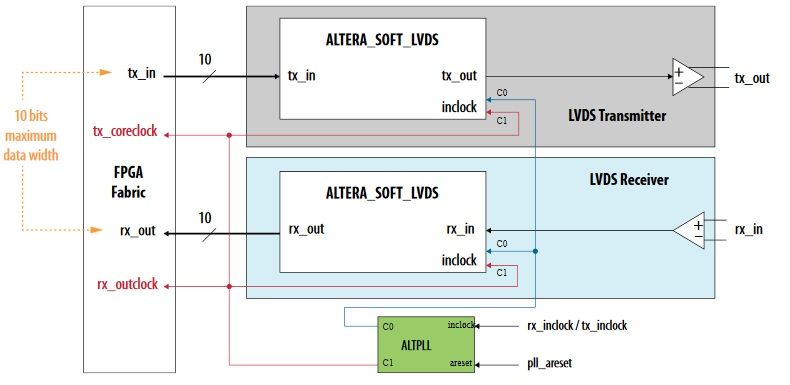

I am reading the Soft LVDS documentation (UG-M10LVDS | 2017.12.15) and some things seems strange:

- The block diagram on Figure2 shows that two clock sources (slow and fast) should be connected to soft serdes block. But i was not able to generate such a block. The generated block always requires fast clock only.

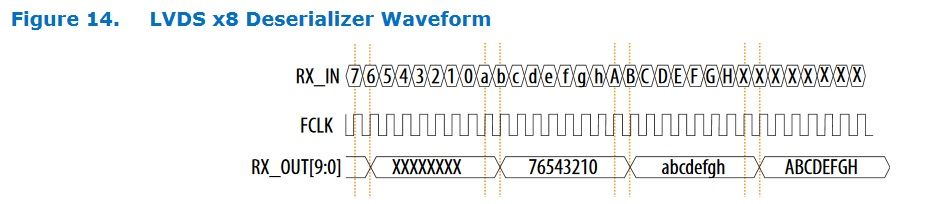

2. The waveform for x8 deserializer shows 10 bit RX_OUT[9:0], but the data is 8bit only. FCLK frequency is the same as data rate frequency, but when you generate the Soft LVDS block in Quartus, it shows a massage that the FCLK should be data rate frequency/2.

Regards

Klemen

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi ,

Kindly find the inline answers

Point no: 1 >> Those fast and slow clocks can be seen from the timing report not from the from the parameter setting of the serdes IP

Reference page no: 33

https://www.intel.com/content/dam/www/programmable/us/en/pdfs/literature/hb/max-10/ug_m10_lvds.pdf

Point no:2 > FCLK should be data rate frequency/2 , Where do you find the information.

Point no:3 > Intel FPGA does not recommend to write own logic for serdes, so do not have any documentation for the reference.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Thank you for your reply.

1: Still it is no clear to me - is the slow clock required for the soft LVDS to function properly or not? I could not find the slow clock also on the Technology Map Viewer. From the block diagram one would assume the serdes can be synchronized to slow clock, but as i understand it, this is not possible to acommplish. The proper synchronization can be achieved with bitslip function and test data only?

2. When you generate a Soft LVDS block you get some info:

Info: lvdstest: Using the external PLL mode requires that:

Info: lvdstest: (i) The fast clock (running at data rate /2) from the PLL feeds rx_inclock

Info: lvdstest: (ii) The outputs be registered in the logic fed by the receiver

Info: lvdstest: The receiver starts capturing the LVDS stream at the fast clock edge

3. I just tried a simple code and it seems it works just fine.

read_serdes_manual : process(clkfast_serdes)

begin

if rising_edge(clkfast_serdes) then

clkslow_serdes_last <= clkslow_serdes; -- edge detection

rx_dv <= '0'; -- default

rx_serdes_data <= rx_serdes_data(6 downto 0) & rx_serdes_i;

serdes_bit_cnt <= std_logic_vector(unsigned(serdes_bit_cnt) + 1);

if clkslow_serdes = '1' and clkslow_serdes_last = '0' then -- rising edge on slow clock

serdes_bit_cnt <= x"0";

end if;

if serdes_bit_cnt = x"1" then -- set fixed offset

rx_data <= rx_serdes_data;

rx_dv <= '1';

end if;

end if;

end process;

Regards

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi ,

To answer your question , training pattern is required for synchronization

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi ,

Kindly let me know, if you need further assistance.

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page