- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

We are facing a problem programming S10 via JTAG.

Example designs: DDR4 and PCIe AvalonST.

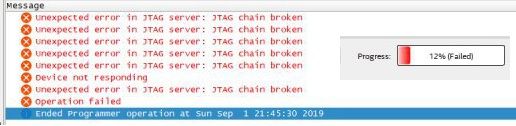

Messages:

18950 Device has stopped receiving configuration data.

18948 Error message received from device: Device is in configuration state.

209012 Opreation failed.

What should we check?

SVID mode: PMBus master

Clock source: Internal Oscillator

All voltages are in range and stable.

Quartus 19.2

S10 parts:

1SG210HU2F50E2VG

1SG280HU2F50E2VG

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Eugene,

There is a known issue which user will have this error message when PCIe and DDR is used in the design. Can you please check if reference clock is supplied appropriately to this IP?

https://www.intel.com/content/www/us/en/programmable/support/support-resources/knowledge-base/component/2018/error-18948---error-message-received-from-device--detected-inter.html

Regards,

YL

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Reference clock is supplied in DDR4 design.

Blinking LED design failed at 12% with JTAG errors:

Previous errors were at 9%.

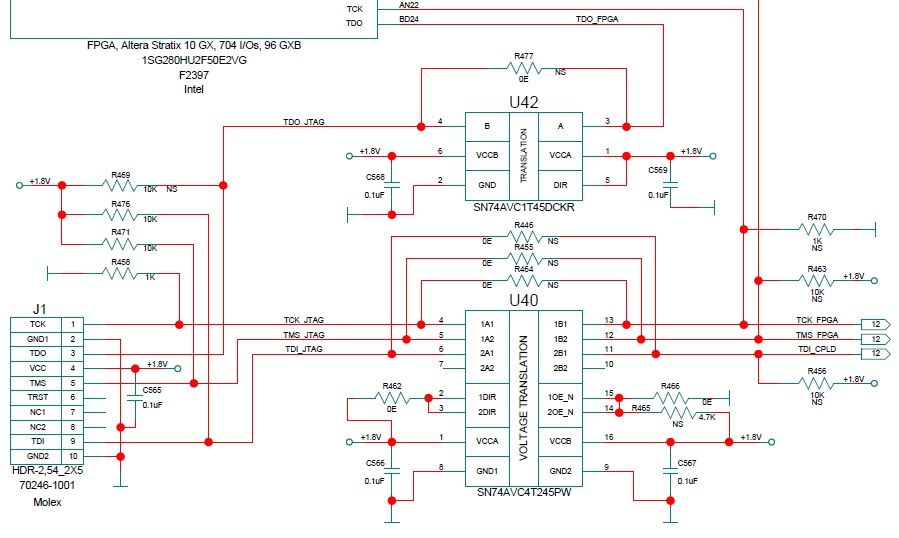

We are using SN74AVC4T245PW level translator as a protection buffer.

Programming hardware: USB ByteBlaster.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Eugene,

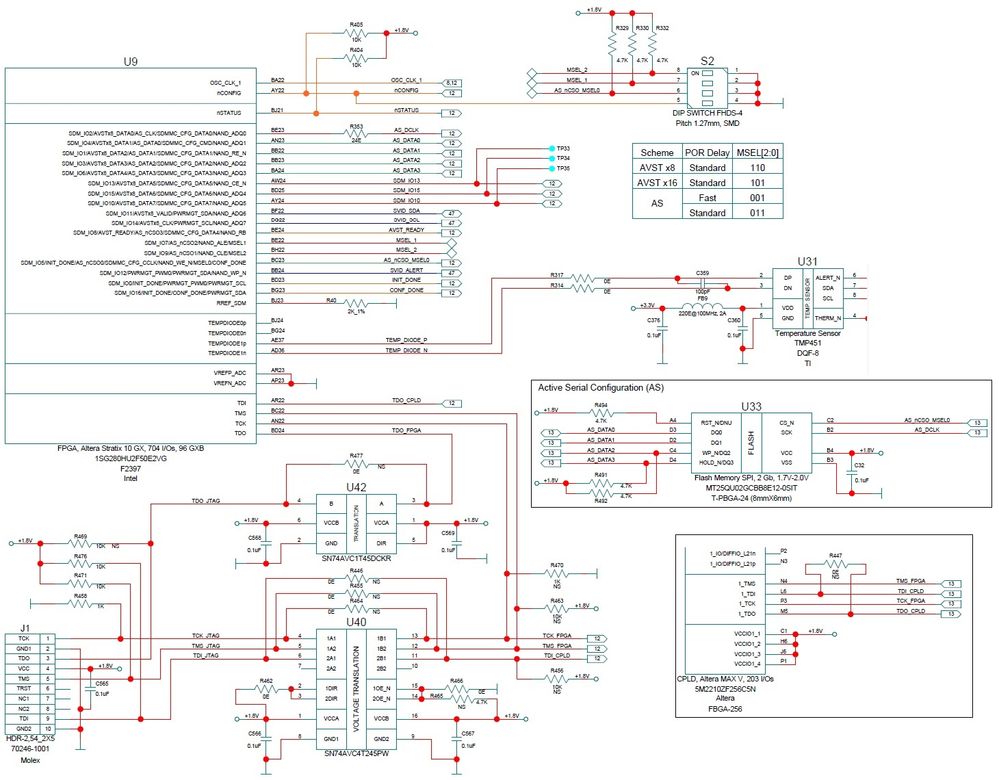

May i know what is the configuration scheme that you are using? Also, can i have wider view on the schematic? The connection between JTAG 10 header with FPGA?

Regards,

YL

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Main scheme is AVST x16.

Flash devices are empty at the moment. We use JTAG only.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Eugene,

May i know are you using our Stratix 10 GX development kit? Can you try to change the MSEL to JTAG mode? MSEL: 111.

Regards,

YL

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

We have a custom board.

Changing MSEL had no effect.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Eugene,

This is weird. Can you ensure that the reference clock is supplying the clock frequency correctly to your PCIe and DDR? Also, can you try to change the TCK frequency to 6MHz? If it is not working either, try to use another piece of USB Blaster?

Thank You.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

The problems were:

- No OSC_CLK_1 was provided.

- VccINT sense is being connected to 4th channel of Power manager (LTC2977). Swapping sence lines with Channel 0 by wires has almost solved the problem. All tests designs were loaded to Stratix and work fine.

But the rest of the problem is wires. It is impossible to hand boards to customer with wires around the board. Quartus has no means to select PM Channel other than default 0.

Is it possible to swap default PM channel by some constraints?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Eugene,

Which PM channel are you referring to? Are you saying the PMBus 0 and etc? If it so, it can be changed, however with limited selection. You can do that in Quartus.

Meanwhile for the wiring part, it is not recommended to do so due to robustness of the board. However, you will need to check with the customer and see whether they accept it or not.

Thank You.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

Power Manager LTC2977 (address - 0x5C) is the only device at S10 PMBUS.

VccINT is at sence channel 4.of LTC2977.

Vcc1.8 is at sence channel 0.

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page