- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

I am using an eval board from Texas Instruments (TSW1400evm). I am trying to implement altpll+altlvds_rx and running into an issue. Clock pin goes into pins AA7 and AA6 which are dedicated clock inputs. I set up the PLL using altpll and also altlvds_rx. When I tried to compile the code, I get the following error messages

Error (176562): Can't place Left/Right PLL "pll_adc_data_acq:inst24|altpll0:adc_pll_config|altpll:altpll_component|altpll0_altpll2:auto_generated|pll1" in PLL location PLL_B1 because the location does not accept Left/Right PLLs Error (176563): Can't place Left/Right PLL "pll_adc_data_acq:inst24|altpll0:adc_pll_config|altpll:altpll_component|altpll0_altpll2:auto_generated|pll1" in PLL location PLL_L2 because PLL has a location assignment that is incompatible with the PLL location in the device

Error (176161): Can't place input clock pin clk_lvds_rx0_p driving fast PLL pll_adc_data_acq:inst24|altpll0:adc_pll_config|altpll:altpll_component|altpll0_altpll2:auto_generated|pll1 in non-compensated I/O location AA7 -- fast PLL drives at least one non-DPA-mode SERDES

Error (176562): Can't place Left/Right PLL "pll_adc_data_acq:inst24|altpll0:adc_pll_config|altpll:altpll_component|altpll0_altpll2:auto_generated|pll1" in PLL location PLL_T1 because the location does not accept Left/Right PLLs

I looked at the reference code from TI and they are doing exactly the same thing. Reference code provided by TI compiles fine. Only difference is their code is in verilog and I am converting this into VHDL and adding more code to do some specific testing. I tried forcing the compiler to choose PLL_R2 using assignment editor and still get the same error. Can someone please let me know, how to fix this?

Thanks in advance,

Regards,

Ramakrishna

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Sree,

if you look at the schematic, dclk from adc goes to pins AA7 and AA6 which comes from pins 56 and 58 from the ADC interface (J3A). In the altpll megafunction, it comes up with the suggestion for Left/Right pll and I compiled the design and this translates to PLL_R2. I haven't changed any pin mapping. If I don't add altlvds_rx, the design compiles and maps to the same location. When I include the altlvds_tx with the clock coming from altpll, it gives the errors I included in the original message

Ramakrishna

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

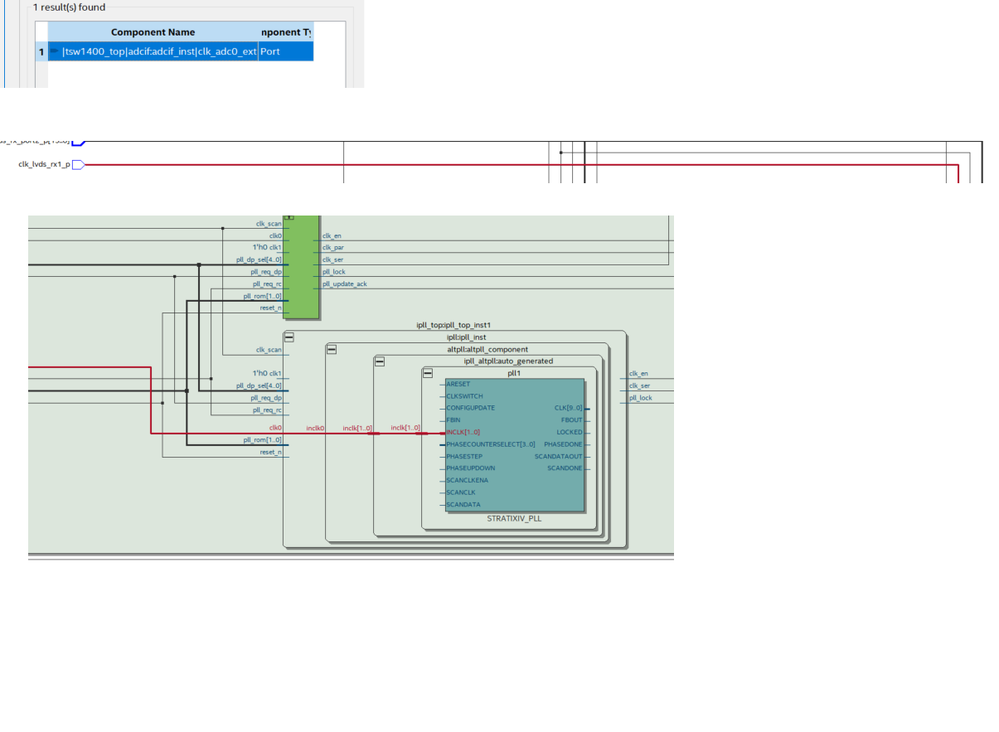

Eventhough ADC interface use the DCLK , from the TIEVM design looks LVDS which is connect to ADC is using LVDS clock .I am looking into the RTL viwer , Here is the screen shot for your reference . If you would like to use the right / left pll kindly request you select the right bank pll for coressponding LVDS channel.

Also let me know how i can help you further to sort it out ?

Thank you ,

regards,

Sree

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Sree,

not sure what are you looking at. TSW1400EVM calls the clock DCLK on the schematic which is mapped to clk_lvds_rx0_p in the code and it is on the pins AA7 and AA6 which is connected pll_R2. When I create the megafunction, it shows it has to be implemented in Left/Right PLL and it is fine without the altlvds_rx component. It maps to pll_R2. As soon as I add the serdes component, it complains about pll which drives non dpa-mode serdes is driven by an uncompensated input. I am not sure how to fix this error and what is causing it

Ramakrishna

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello Ramakrishna ,

If you plan to use the non -DPA mode , PLL which is driving the non-DPA mode SERDES should be compensated . LVDS Compensation option will be there in the PLL IP setting .In Non-DPA mode you have to make sure DATA and CLOCK compensate for the SKEW.

can you kindly refer below link document ? which contain full insight of LVDS SERDES IP. " Table 20 "

https://www.intel.com/content/dam/www/programmable/us/en/pdfs/literature/ug/ug_altera_lvds.pdf

I thought you were just converting Verilog to VHDL from the TI example design .

Thank you ,

Regards,

Sree

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Sree,

I selected the option of "In source-synchronous compensation Mode" and I still get the same error. I tried all possible options and I still get the same error. I can send my code, if it helps looking into this issue. Please let me know

Thanks,

Ramakrishna

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello Ramakrishna,

Sorry , I didnt get notification that you replied and I am just cross verifying something else i came across your post .

Can I know did you find a way to fix this issue ? if not , Can you send the files and I will look at now ?

Thank you ,

Regards,

Sree

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Sree,

I am attaching the code along with this replay. I was using Quartus 13.1 to compile the code. Please let me know, if you find something

Thanks,

Ramakrishna

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

13.1 is older version ....I will try and let you know :)

Thank you ,

Regards,

Sree

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello Ramakrishna ,

Today i get chance to look at the file ,

I removed your pin assignment in the editor and try to build. It complies fine ....Can you check the pin assignment by default Quartus fitting with which location to the PLL and cross verify with yours ?

Thank you ,

Regards,

Sree

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page