- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Intel,

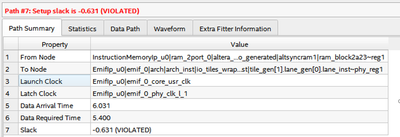

I got timing violated from emif_core_usr_clk to emif_phy_clk_l_1. Is it possible to set false path for emif_usr_clk to any emif_phy_clk?

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

More details definitely needed. What's your target device? What are the parameters for your EMIF? Hard or soft implementation (device-dependent)? Stand-alone IP or are you implementing it in a system in Platform Designer? Etc.

You do not want to false path this if it's a transfer between the core and the interface, so you need to find the root of the violation.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

1. My target device is DDR4 Hilo module on arria 10 FPGA.

2. The EMIF parameter is follow standard DDR4 Hilo module type.

3. Hard IP for implementation.

4. I designed a system with EMIF DDR4 IP.

I think the emif user clock is only for others FPGA elements using because there is fifo between the emif user clock and emif phy clock. So they do not have any relationship. Is it right?

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page