- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I'm working on a bare metal application on a Cyclone V SoC (5CSEBA6U23I7NDK).

Things are going reasonably well, I have the u-boot SPL booting from eMMC on power-up and it's loading my application. I can read from eMMC and successfully load the FPGA image using the FPGA manager.

Where I'm stuck now is enabling the HPC to FPGA bridge. I have that bridge as well as the lightweight bridge enabled in my qsys design. They're both connected to a very simple Avalon memory mapped slave that I've used in previous designs and know works. However, any time I try to read from the FPGA at address 0xC0000000 my HPC locks up.

I have made sure that the two bridges are both not being reset by the reset manager. Is there any other critical setup that I need to do on these bridges to get them working? I feel like there's some simple thing that I'm missing.

Any suggestions would be appreciated.

- Steve

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

OK, after many hours of head scratching I think I found my problem.

To use the HPS->FPGA slave you need to set bit 3 of the remap register located at address 0xFF800000. To use the lightweight bridge you need to set bit 4 of this register.

Seems to be working now!

S

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Assuming you're using HWLibs, did you issue alt_bridge_init?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Thanks for the response. I'm not actually using the hwlibs, but did read through the code for alt_bridge_init and I think I'm doing everything that it does (which isn't really much other then take the bridge out of reset). I'll keep looking.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi SGlow,

If you are booting up with U-boot, can you try to execute "bridge enable", it is one of the cmd available in U-boot. Can check whether it is available by typing help in U-boot.

After execute "bridge enable", can use md to check the address content. Example to check the address content, md 0xC0000000.

Thanks.

Regards,

Aik Eu

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Aik Eu,

I'm only using the u-boot SPL, not the full boot loader. The SPL just does initial configuration of the SDRAM and some other areas of the HPS and then jumps to my code. The SPL doesn't have any type of user interface, so I can't use it to configure the bridge.

I've been doing more investigation into this issue, but am still getting bus fault exceptions any time I try to access the memory space of either the HPS->FPGA bridge or the lightweight bridge.

I've found that even trying to access the register space in the lightweight bridge results in a bus fault exception. For example, the read only ID registers located in the lightweight bridge at 0xFF401FD0, 0xFF401FE0, etc. Attempting to read any of these registers results in a bus fault.

I have confirmed that the FPGA image is properly loaded and the FPGA is in user mode. I also confirmed that I have taken the two bridges I'm trying to use out of reset in the reset manager. I have the l3_main_clk enabled and running at 400MHz, the l4_mp_clk clock enabled and running at 100MHz, and I've got both the h2f_axi_clock and h2f_lw_axi_clock connected to running clocks in my FPGA design.

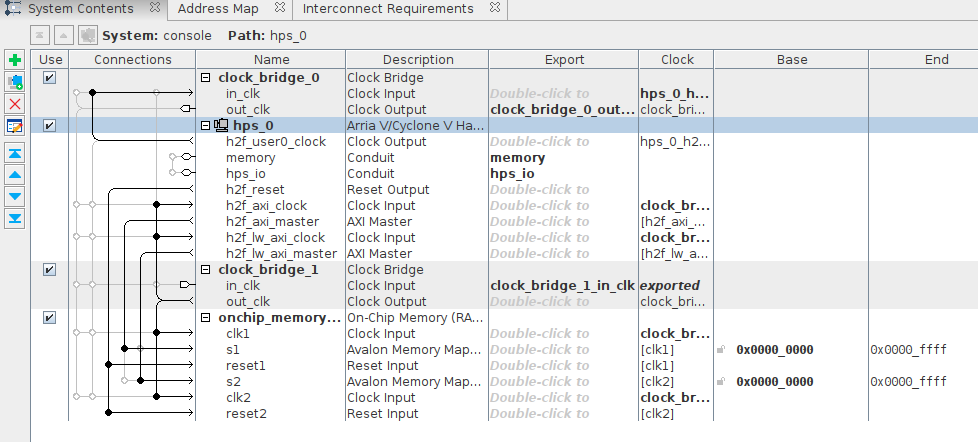

I replaced my own avalon slave module in the qsys system with a dual port internal RAM block. That removes any of my own design from the qsys system for now. Here's what my qsys design currently looks like, I have attached the qsys file as well.

I'm pretty stumped by this. Let me know if you can think of anything else that I could try.

Thanks,

Steve

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

OK, after many hours of head scratching I think I found my problem.

To use the HPS->FPGA slave you need to set bit 3 of the remap register located at address 0xFF800000. To use the lightweight bridge you need to set bit 4 of this register.

Seems to be working now!

S

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi SGlow,

Good to know that you have resolved the issue on your side. Thanks a lot for the sharing in your findings.

For my own understanding, I have tried to checked the bit that you set in order to see if it is the same as bridge enable in U-boot. However it only allows write only but not read for remap register. Anyway when I set that particular bit using mw.l in U-boot but, seems that the bridge enable does not happened....

Anyway, I will close this thread for now since the issue has been resolved on your side.

Thanks.

Regards,

Aik Eu

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page