- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Here is the device I use:1SG280LN2F43I2LG

There are several phenomena:

1. if I choose the option of allow retiming register, the data output will be wrong or no data ,with good timing closure. however, I don't choose the option, data output is right ,with bad timing closure.

2. I use the dont_retime attributes for part of modules , the result may be right or wrong at different frequencies .

I need your help with my problem , thank you.

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

If you're meeting timing, but not getting the outputs you expect, then chances are your design code is not doing what you intend. Perform a functional simulation or use a hardware debug tool like Signal Tap to verify the design in hardware.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Thanks your answer !

The output of functional simulation is meetting my expect, but my understanding is that retiming the register will not change the logic,Isn't it?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

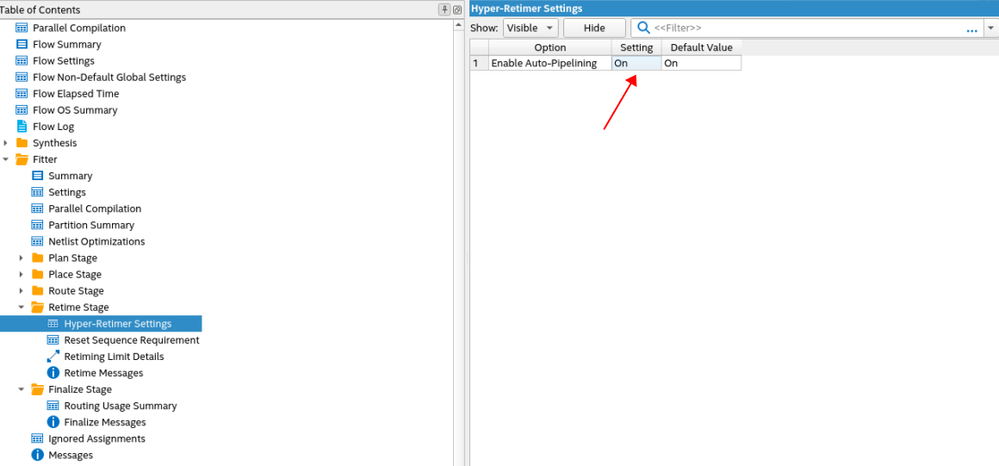

No, register retiming does not change logic function. You are using a Stratix 10 device, so make sure you have hyper-retiming enabled. That will work better with a Hyperflex device than the standard register retiming.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I did not find the option of hyper-retiming in Quartus 20.4.

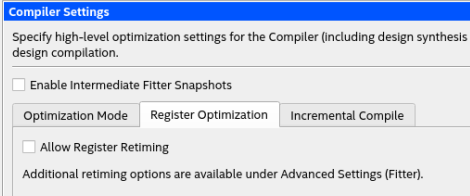

Can this show that it has been turned on ? the screenshot below.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

That's not the right setting. Go to Assignments->Settings->Compiler Settings->Register Optimization and make sure "Allow Register Retiming" is checked.

Regards,

Nurina

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Nurina,

Thanks for your answer.

You should scan the record above, my problem is that as long as this setting is turned on, the data output is wrong .And I have tested my code in xilinx vu9p with no wrong .Because this project is big, so hardware debugging will take me a lot of time.

Can your team help give some suggestions?tks.

Best regards,

Michael

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Michael,

Well if it's not functioning as expected with re-timing then there must be some issues with your code, or you missed some steps during migration. Are you sure you're using the correct compiler settings? Have you set the same Verilog/VHDL version as in Vivado? What steps did you take when you migrated from Vivado to Quartus?

Regards.

Nurina

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Michael, do you have any updates?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

We did not receive any response to the previous question/reply/answer that I have provided, thus I will put this case to close pending. Please post a response in the next 15 days to allow me to continue to support you. After 15 days, this thread will be transitioned to community support. The community users will be able to help you with your follow-up questions.

Regards,

Nurina

P/S: If you like my comment, feel free to give Kudos. If my comment solved your problem, feel free to accept my comment as solution!

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page