- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Software version:Quartus Prime Lite Edition 18.1

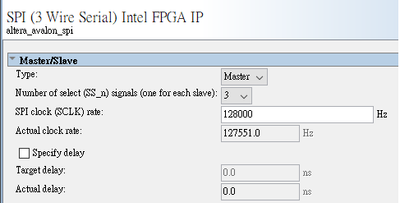

I would like to let DE0-Nano be a SPI Master to control 3 SPI slave.

I add SPI IP and set ss_n as 3.

After generating verilog file, there is only one xx_external_SS_n in xxx_inst.v for user.

Is it a bug?

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi!

First of all, thanks for reaching us,

regarding your question, the reason why it seems to be just one xx_external_SS_n in the *_inst.v file it's because appears as an array, not as individual connections.

if you navigate to Soc_system -> synthesis ->submodule_spi.v you'll find that its declared as 'output wire [2:0] spi_o_external_ss_n'.

Please let me know any questions you may have.

Regards,

-Eliath Guzman

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Thanks for your reply.

I defined the pin as 2 bits, and it works well.

Many thanks.

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page