- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

can the pll locked signal of the max10 be used as the reset signal ?

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Zhang Lan

In general, we don't want to use the PLL lock signal as the reset signal directly. The reset will be an asynchronous reset and some of the PLL lock signals may toggle for a while before they stay in a static state. You must ensure that the asynchronous reset is debounced and filtered. You can refer to Asynchronous Reset section in the link below:

https://www.intel.cn/content/dam/altera-www/global/zh_CN/pdfs/literature/hb/qts/qts_qii51006.pdf

thanks.

Eng Wei

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Thanks for your help,

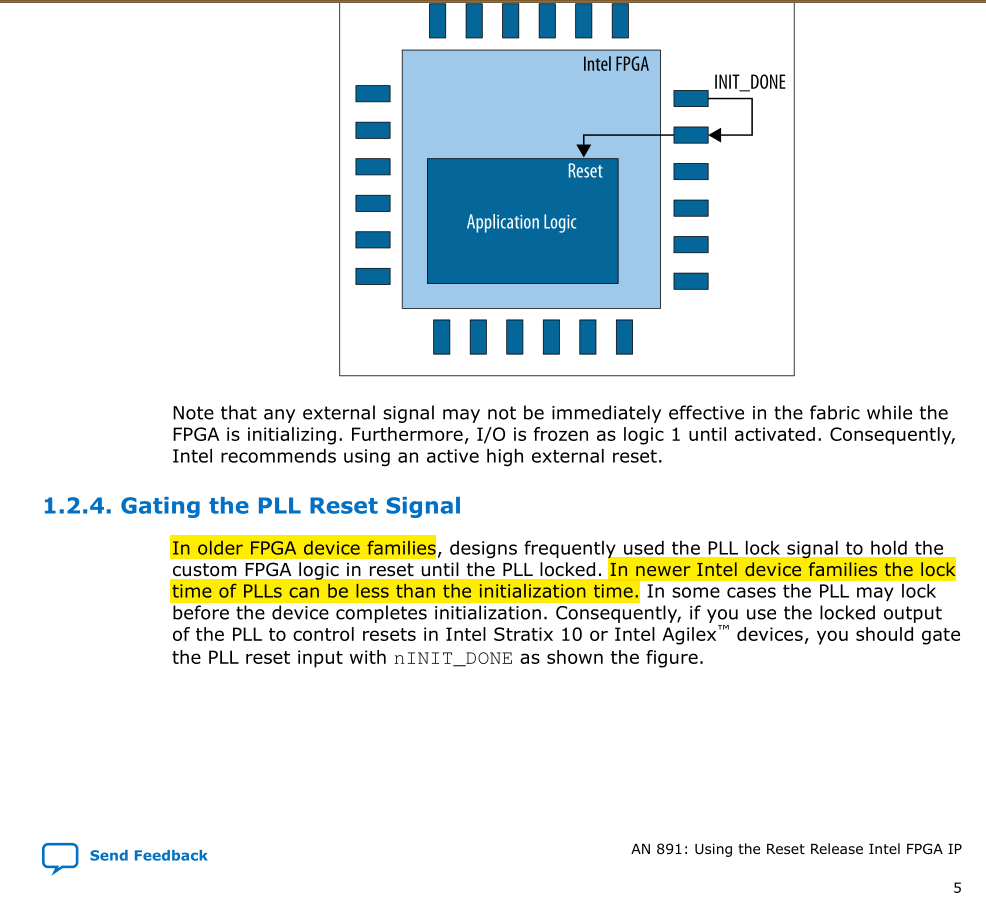

and the information mentioned in the figure below applys to max10 or not ?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

and there are no INIT_DOWN and nINIT_DOWN signal, is there any other signal can be used as the init done signal for the max10 ?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

that is I want to implement the similar reset circuit shown in the above figue in page 5 of AN 891, can I ?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Zhang Lan

Nope, this pin isn't available for Max10. Designers typically use an explicit reset signal for the design, which forces all registers into their appropriate values after reset. Intel recommends this practice to reset the device after power-up to restore the proper state.

thanks.

Eng Wei

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Zhang Lan

We do not receive any response from you to the previous answer that have been provided. This thread will be transitioned to community support. If you have a new question, feel free to open a new thread to get the support from Intel experts. Otherwise, the community users will continue to help you on this thread. Thank you.

Eng Wei

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

and what is the explicit reset ? can you give me an example? please

the meaning of explicit is indistinct,right ? and how can I get a indistinc reset?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Zhang Lan

It means you can use an external pin to initialize the design upon power-up. The reset pin is just similar to any other input pin and is often applied asynchronously to the FPGA. As long as the duration of this global reset pulse is long enough, all the device flip-flops will enter the reset state.

You can find some other good sites for reading and I attached one of the Intel one:

Thanks.

Eng Wei

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page