- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Quartus prime version 20.2.0 build 50 06/11/2020 SC pro edition, free 30 day license.

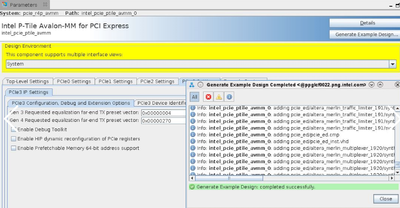

Following the instructions shown in section 5.3, "generating the design example", in the document of "Intel FPGA P-Tile Avalon Memory Mapped IP for PCI Express Design Example User Guide", ug-20268 | 2020.07.10, I tried to create a PCIe RP IP, see the attached ip file of "pcie_rp_avmm.zip", but failed in doing the step#13 with the errors shown in the attached "received_error.log" file.

The test project file is created targeting to the device AGFB014R24A2E3VR0, but the log message, line#16 in the received_error.log, shows that the AGFB014R24A2E2VR0 is used in creating the PCIe RP IP code.

The RP IP is set to target to the Agilex F-Series P-Tile FPGA Development Kit, but the log message on line#11 shows "Targeting Stratix 10 FPGA Development kit ...."

The error, shown on line#38, looks like a tool internal failure.

Also in the adding device menu in creating a project, there is no way to add in the Agilex F-Series development Kit board.

I would like to know if the ptile-pcie-avmm ip, in x4 RP mode, has been fully tested in Intel's lab or not?

Thanks,

Xiao

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Sorry, I overlook the dev kit setting. After putting the Agilex dev kit and generate the ED, the design files look bigger so I can't directly attach to here.

Here is the step to get the file:

Install Filezilla that can download from here:

https://filezilla-project.org/download.php?type=client

After installing, launch the tool and login as below:

Host: secureftp.intel.com

Username: tmp01481

Password: W@ng1234

Port 21.

You can see the zip file is located at the right of the window. Name = wang_ag.zip.

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Sir,

The Generation fail is due to "Enable PHY Reconfiguration" option is turned on. I opened the attached .ip file turn on the option and the generation is successful.

This is a known issue that generation will fail when you turn on the option. This issue will fix in future quartus version.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

It is still not working on my side. I deleted the whole old project folder, and re-did the generation from beginning. I am sure the "enable phy reconfiguration" option is off in GUI this time. But the generation is failed almost in the same way as last time, the error messages and ip file are attached.

The log message shows that the device part number and the development kit board used in the generation are still not matching with the settings. For me it looks like the generating tcl does not sync the system settings.

Since it is working on your side, I worry that some of the tool settings may not be right on my side? As I mentioned before, there is no way for me to set the development board in new project wizard (the board tab is empty).

regards,

Xiao

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello Sir,

I open your latest attached. ip file and generate the example design from there. The generation is successful.

I believe the Agilex Example design (ED) is create based on the faster speed grade for now, so no matter what device that you set in your project, the example design will generate based on the device AGFB014R24A2E2VR0.

Just want to let you know that the support for Ptile PCIe IP in Agilex is still in prelim stage, thus it might not cover across all speed grade.

At this moment, do you want me to send you my generated example design so that you can use it directly without generation?

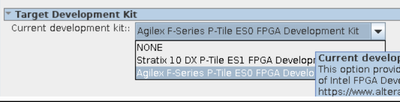

Also, are you mentioned that the “Current development kit” in your GUI is empty? From my side, I can see “none”, “S10 DX” and “Agilex”.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

By the way, are you able to generate the standalone IP? Also do you try to generate other IP's ED?

- Tags:

- he way

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I am new in using the Quartus tool and the first practice is to generate the PCIe RP IP. So I have not do any other IP-DE yet.

regards,

Xiao

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I think the example design generation failure is caused by a bug in adding in the module of clock_crossing_bridge. The error message, at line#40 shown in "received_error_2.log" attached previously, shows,

Error: add_fileset_file: No such file C:/Users/PC_LAB_FPGA1/AppData/Local/Temp/alt8499_1907179446840489927.dir/0001_intel_pcie_ptile_avmm_0_gen/ip/pcie_ed/pcie_ed_clock_crossing_bridge/altera_avalon_mm_clock_crossing_bridge_1920/synth/pcie_ed_clock_crossing_bridge_altera_avalon_mm_clock_crossing_bridge_1920_fdcxukq.v/pcie_ed_clock_crossing_bridge_altera_avalon_mm_clock_crossing_bridge_1920_fdcxukq.v

The file name of "pcie_ed_clock_crossing_bridge_altera_avalon_mm_clock_crossing_bridge_1920_fdcxukq.v" is inserted two times in the file searching path.

(But the message at line#38-39 shows that the other two rtl files, "*dc_fifo_1920_qcx4w5q.*", in the same folder were fetched correctly.)

regards,

Xiao

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

In the "IP Parameter Editor Pro" window, when I clicking the "Generate HDL ..." control button located at bottom-right corner, the generation is always successful no matter of the "Enable PHY Reconfiguration" selection. But when clicking the "Generate Example Design ..." control, the generation are always failed no matter of the "Enable PHY Reconfiguration", or the "Current development kit" or the "Design Environment" (standalone/system) selections.

The Agilex F-series development kit, intel PN# DK-DEV-AGF014E3ES we purchased, has the device of AGFB014R242E3VR0 installed. The current released version of Quartus tool has to be able to support it. I saw the log message shows that the generation uses AGFB014R242E3VR0 sometimes, but not always. I saw the both of AGFB014R242E3VR0 and AGFB014R242E2VR0 devices are listed in the *.ip file, which looks not right for me.

I am able to see the "none, stratix, agilex" options in the "Current development kit" control, and I set to use the agilex developemnt kit. I saw your log message, "ptile_generated.txt", shows that the generation is targeting to Stratix 10 development kit, but the device is AGFB014R242E2VR0, which looks so wrong for me. I made a test by selecting the Stratix 10 development kit, the log message shows that the tool changed the device to 1SD280PT2F55E2VGS1.

If I open the "Device Family" window, the device setting shows the right values of "Agilex" and "AGFB014R242E3VR0". but why the "Stratix 10" development kit still shows up in the generating option?

The "Current development kit" has the "Agilex F-Series" development kit option, but I do not see how and where this board is set in the tool. When following the document ug-20268, section 5.3 to run the "file->new project wizard", in the "family, device & board" setting page, the "board" tab is empty. I believe the Agilex-F development board should be shown here, but I could not find out how to add it in.

Could you please help to generate a RP IP with example design for me by using the following settings,

family : Agilex

device : AGFB014R242E3VR0

development kit : Agilex F-Series

IP : intel-pcie-ptile-avmm

Design environment : System

Hard-IP mode : Gen4x4, interface - 128 bit

Port-Mode : Root Port

PLD Clock Frequency : 350 MHz

Example Design Files are for Synthesis only in verilog format targeting to Agilex-F development kit.

Then let me know how to download the whole design folder.

Thanks,

Xiao

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Downloaded the zip file, thank you very much for the help. I am learning it now.

I saw that in the .ip file the the "current development kit" option is set to "none" instead of the agilex board. Any reason for doing it? For my understanding, the example design should target to a board in order to correctly assign the design IO pads locations. What should I know about this?

Thanks,

Xiao

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Sorry, I overlook the dev kit setting. After putting the Agilex dev kit and generate the ED, the design files look bigger so I can't directly attach to here.

Here is the step to get the file:

Install Filezilla that can download from here:

https://filezilla-project.org/download.php?type=client

After installing, launch the tool and login as below:

Host: secureftp.intel.com

Username: tmp01481

Password: W@ng1234

Port 21.

You can see the zip file is located at the right of the window. Name = wang_ag.zip.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Downloaded the zip file without issue, thanks.

Learning the design, and have one question about the port assignment. The PCIe RP IP has four RP x4 bifurcation, and only the P0 core is exported in the design, which is assigned to PCIe lane#0-3 in the "pin planner". But according to PCIe IP document, UG-20237 table-57, the P0 is mapping to the PCIe lane#4-7 (instead of lane#0-3) in P-Tile 4x4 mode. I am so confused about the mapping between port# and core# by this example design.

Thanks.

Xiao

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Thanks I can see you post the new question in the new thread.

I will get back to you on the new thread soon. Thanks.

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page