- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

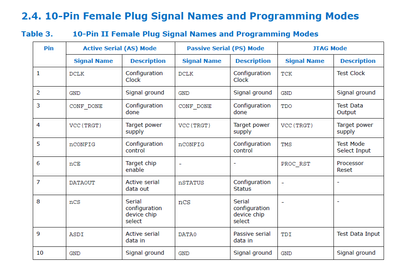

where should pin 6 of usb blaster ii cable to connect for FPGA max 10 and Cyclone IV?

Using JTAG mode, pin 6 proc_rst

Should it be some pin user defined for system reset?

Any dedicate pin of FPGA?

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

You may use pin 6 for hard processor reset under JTAG mode. Otherwise, you may leave it unconnected.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

what do you mean hard processor reset?

Should it be a pin user defined for system reset in verilog code?

Any dedicate pin of FPGA?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Yes, it is a pin used to trigger warm reset of the HPS block when prompted via the ARM DS-5 debugger in JTAG mode, It depends whether if you are using that or not. Else you may leave it unconnected.

As per the note in USB Blaster II user guide, you are recommended to connect this pin to a secondary device such as the MAX V CPLD, and use the device to manage the reset network for HPS.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Which pin?

Device is 10m16DCU324I7G

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

It can be any pin in the MAX 10 since it is programmable. As long as the logic will trigger warm reset to HPS.

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page