- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

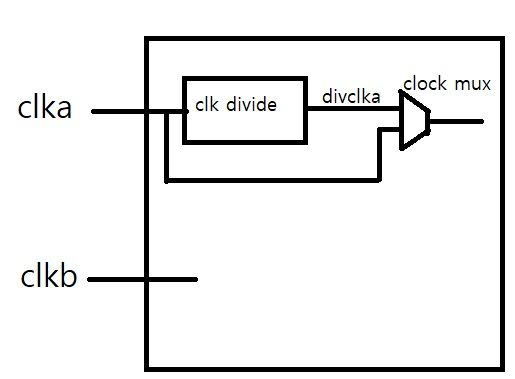

There are clka and clkb (asynchronous source),

divclka is made from clka,

and there is clock mux ..

i contrainted them like below,

create_clock -name { clka } -period 10.0 [get_ports{ clka }]

create_clock -name { clkb } -period 10.0 [get_ports{ clkb }]

create_generated_clock -name { divclka} -divide_by 2 -source [ divin* ] [ divout*]

create_generated_clock -name { clkc} -master_clock { divclka} -source[ divout* ] [muxout*]

create_generated_clock -name { clkd} -master_clock {clka} -source[get_ports{ clka }] [muxout*] -add

==> set_clock_group -asynchronous -group {clka divclka clkc clkd }\

-group {clkb}

set_clock_group -exclusive -group {clkc}\

-group {clkd}

I included underlined clkc and clkd in the same group. Because clka, divclka, clkc, and clkd are all produced from the same clka, so they are thought to be the same clocktree.

And clkc and clkd are set to exclusive.

So, I wonder if the -asynchronous -group {clka divclka clkc clkd } and set_clock_group -exclusive -group {clkc}\ -group {clkd} both apply, or whether one of them are ignored. Also, please tell me how to modify the code above. Thank you.

(* is a name made up)

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Clock groups provide a advantageous way to specify the clock are not related.Asynchronous clocks are completely unrelated that is two clock generated from the different source. Exclusive clock means not used at the same-time in the design , but not clock can exists but not used i would say in your case is mux output.

In your case clock group and asynchronous only applicable to the clka and clkb, but exclusive can apply to the clock mux output.

set_clock_groups --asynchronous -group {clka divclka clkd} -group {clkb} (I believe clkc and clka both same)

set_clock_groups -logically_exclusive -group {clka} -group {divclka} : Note I dont know full design , constraint applicable specific path given in the diagram.

Also set the false path since clka and clkb are not related

set_false_path -from [get_clocks clka] -to [get_clocks clkb]

set_false_path -from [get_clocks clkb] -to [get_clocks clka]

Thank you ,

Regards,

Sree

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

The OP doesn't need set_false_path constraints if they use set_clock_groups. That's the whole point and one of the main advantages of set_clock_groups!

#iwork4intel

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page