- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello!

Can you advice me, please, where can i find some log files after i run pcm.exe ?

Thanks.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I usually just redirect the output to a file, i.e.

pcm.exe > pcm.log

On Linux, it is also very simple to print the output at the same time with

pcm.exe | tee pcm.log

Alternatively, you can use the fairly recent file output

pcm.exe -csv=pcm.csv

Kind regards

Thomas

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

pcm.exe does not log anything by default. What are you looking for?

Roman

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I usually just redirect the output to a file, i.e.

pcm.exe > pcm.log

On Linux, it is also very simple to print the output at the same time with

pcm.exe | tee pcm.log

Alternatively, you can use the fairly recent file output

pcm.exe -csv=pcm.csv

Kind regards

Thomas

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Thank so much!

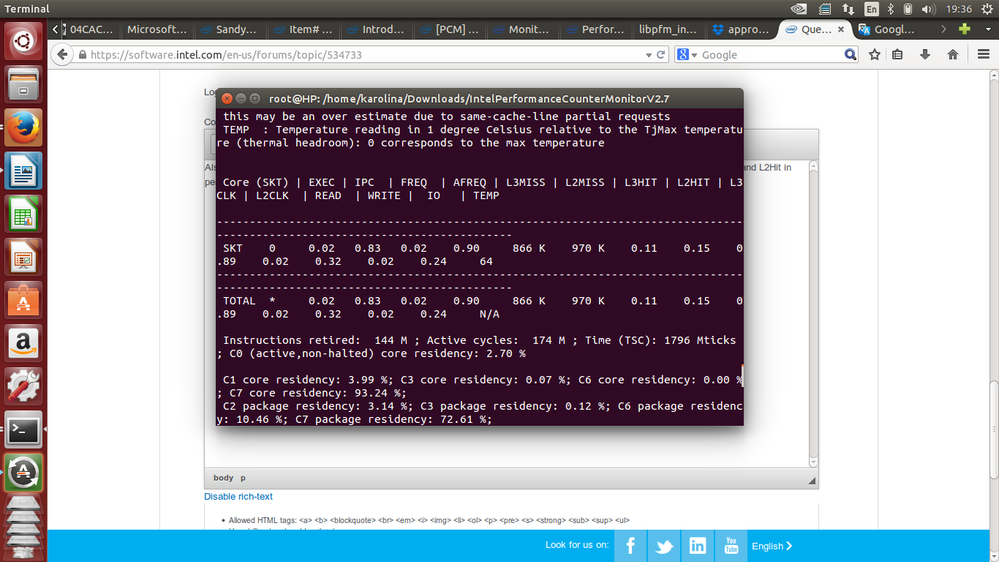

I am looking for how to execute L2 hit/miss and L3 hit/miss. Because of that i've got some questions:

1. Why there is written "L2MISS: L2 cache misses (including other core's L2 cache *hits*)" ? How can i get L2 cahce misses without other core's L2 cache hits?

2. I run pcm.exe on Ubuntu so.. when i write "./pcm.x" i can see the work of all cores but i can't see the parameters for "READ", "WRITE" and "I/O"? And when i use "./pcm.x 1 -ns -nc" I can see "READ", "WRITE", "I/O" but without separation into cores ( only TOTAL data).

Can you advise me how can i fix it?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

1. If the L2 cache is missed on core A, the cache line might reside in some other core. We therefore consider this a miss since the core that requests this cache line does not find it in its own L2 cache.

2. PCM monitors READ and WRITE traffic directly in the memory controller. The monitor therefore does not distinguish between traffic of individual cores but only per memory controller.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Also i didn't get why when i run pcm.exe in Ubuntu terminal i can see the measurements of L3Miss and L2Miss in K and L3Hit and L2Hit in percentages but when i redirect the output to a file i can't understand the dimension of my measurements. (is it still in K for L2Miss and L3Miss, is it still in GBytes for Read and Write)?

Just in case, the output file and screen shot are in attachments.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

When writing to a csv file, values are converted to a standard unit. In normal output, the format varies between K, M, and G, depending on the size. The idea is that the csv output should be simple for automatic processing. The screen output should be simple for human readers.

I'm sorry if this confused you.

In case of cache misses, the csv file prints millions of misses.

You can find a full list of descriptions for the columns in the csv file in this blog.

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page