- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello

I have a i7-13800HRE CPU on COM Express 6 embedded system.

The eSPI port is connected to LPC bridge IC ECE1200 from Microchip using CS1.

When we send I/O cycle, the LFRAME# signal is asserted visible with scope.

However when we set a memory decoding address at ESPI_CS1GMR1 (0xFE000001) and trying to read/write io remapped region, there is no any transfer initiated. This is according Intel 700 Series chipset, volume 2, page 74.

Do you have any idea, why memory transfers are not passed?

Thanks in advance!

Krasimir Kostadinov

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello @krasimirk,

Thank you for contacting Intel Embedded Community.

You can check the following registers:

1.Second eSPI Generic I/O Range (SEGIR) — Offset 27BCh

2.eSPI CS1 Generic IO Range 1 (ESPI_CS1GIR1) — Offset A4h

Best regards,

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

We tried the IO transfer, but the read and write time is 7us for a single byte. According the LPC specification it should be 0.63us for 1 byte transfer in the IO space. This is around 10 time worst.

Any idea why the transfer times are so slow?

Kind Regards,

Krasimir Kostadinov

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello @Diego_INTEL

There is no such register SEGIR in the Intel 700 Series chipset datasheet.

The register ESPI_CS1GIR1 exists.

However both of those registers are related to IO transaction and not memory transactions. We do not have problems with IO transactions, but we do not use them. We have a device which is connected behind LPC bridge and it's FW can only accept memory transaction (not IO transactions).

I will appreciate it very much if you have other idea.

Kind Regards,

Krasimir Kostadinov

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello again

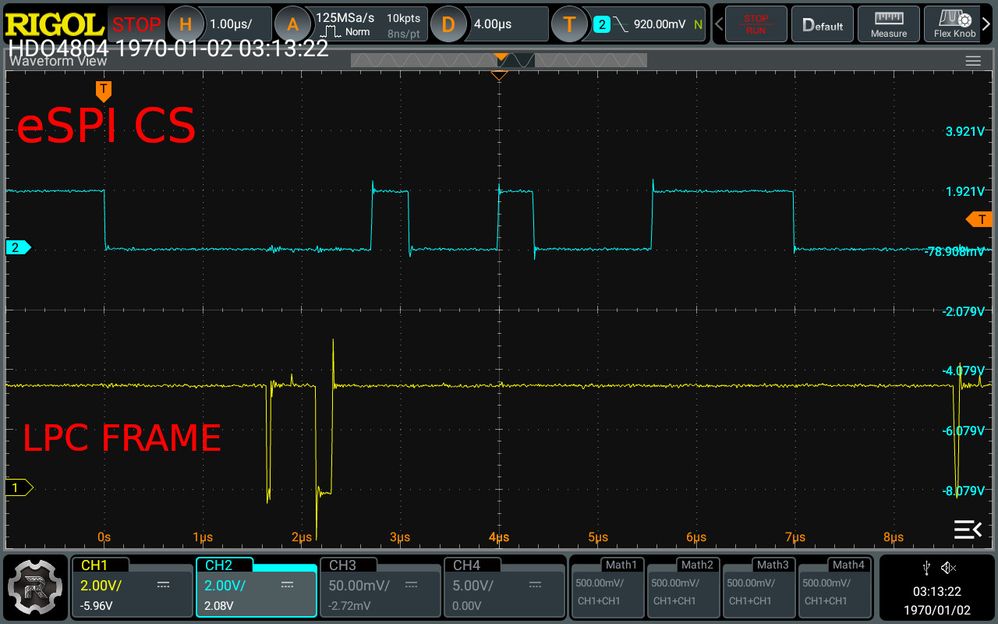

Here is the problem with the IO transaction delays.

On the scope screenshot you can see the CS of the eSPI. Between 2 outb transactions there are exact 7uS delays instead 0.63uS for 1 byte transfer.

Any comments?

Kind Regards,

Krasimir Kostadinov

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello @krasimirk,

You may try looking document #620778 - Tiger Lake-UP3 for IoT Platforms COMe Type 6 Module Customer Reference Board, is a white paper that may help checking the connection and configuration. Note that this is for Tiger Lake, unfortunately there is not a document like this for Alder Lake or Raptor Lake as I'm aware, but still, this may be helpful to check.

Also, you can check that the firmware of the LPC bridge is the latest and is the right one for Intel products, as I looked internally that a firmware update helped in those cases.

Best regards,

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

Could you give me the link for the document? I can not find it in the https://www.intel.com/content/www/us/en/products/platforms/details/tiger-lake-up3/docs.html

The datasheet of ECE1200 eSPI to LPC does not mention anything about firmware update possibility.

Kind Regards,

Krasimir Kostadinov

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page