- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello, We have a custom board with AGIB022R31B2E1V implementing 4 identical EMIF interfaces. When tested with the EMIF toolkit for re-calibration and margining, we got conflicting results. First, both recalibration and traffic test within the toolkit passed.

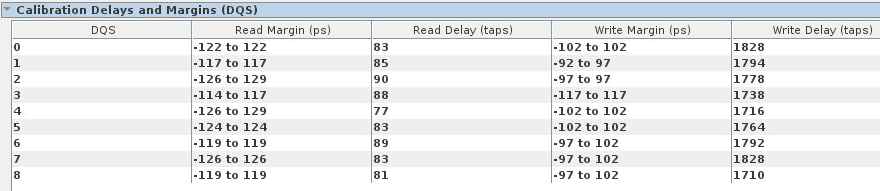

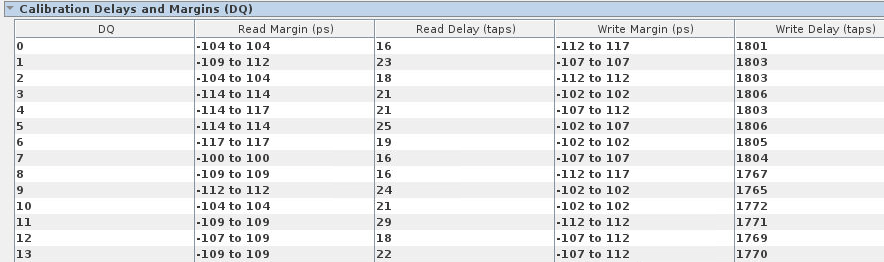

However, the DQS input, and DQ input are all out of place. The read window of 468ps is way over the theoretical 312ps for a 3200Gbps DDR4.

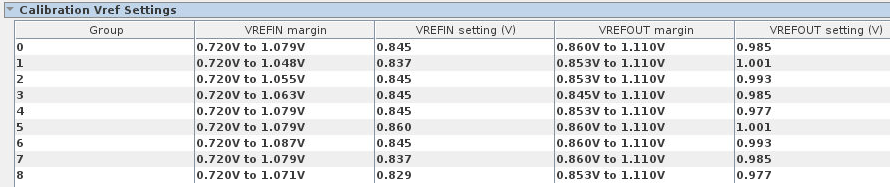

Vref_In calibration result is also unconvincing.

DQS, DQ output and Vref_out calibrations looks correct. Same behavior happened to all 4 EMIF/DDR4.

Memory configurations are:

Does anyone have any idea why the calibration report seems wrong while both re-calibration and traffic test indicated otherwise.

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

Thank you for submitting your question in Intel Community.

I'm Adzim, application engineer will assist you in this forum.

From my point of view, I think your board is healthy based on the result of the calibration and traffic generator status.

You should be worried if there are some issue with calibration report or data corrupting during write or read transaction.

I think the read margin is not 468ps but I need to double check on how to calculate the margin from the EMIF Debug Toolkit.

Do you have any other doubt with EMIF Debug Toolkit?

Regards,

Adzim

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Adzim,

Thank you for your reply. We do have another design/board using the exact same FPGA and EMIF interfaces, but have the correct responses. Please see snapshots below:

Back to the original bad calibration reports, I believe the -234ps to 234ps is the preset values, and I guess something caused the calibration finished pre-maturely and the margins were not updated.

This issue is also filed in https://premiersupport.intel.com/IPS/s/case-detail?recordId=500Ho00001MjUOkIAN&isCase=true

but no owner has been assigned yet. Please see if you can push someone to look into it.

Regards,

Colman

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Colman,

Thank you for your feedback.

Based on your results from two boards, looks like the second board has more accurate result from the EMIF Debug Toolkit.

I want to clarify the test that you have carried out for both boards :

- The design that you have used is a same design or a different design?

- Have you tried to swap the RDIMMs between the bad(first) and good(second) boards?

- Have you tested with single EMIF interface at a time to get the calibration report?

I would need more details to debug this issue but since you have file another case in the IPS, I would like you to choose on which platform that you're comfortable continue the discussion.

Because we are usually discuss a same issue in one platform and close the other open case.

So it's depend on you if you want to discuss this issue in this forum or you want continue the discussion in IPS.

Please let me know your most convenience way.

I will take the action to facilitate this issue.

Regards,

Adzim

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Adzim, Let's discuss this over the IPS platform. I already uploaded more information over there.

Thanks and Best Regards,

Colman

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

The problem is resolved and I just want to close the loop here. The root cause is that the clock driver to the EMIF reference clock was not set up correctly and caused some EMIF channels calibration failures. The confusing part was that EMIF toolkit reported calibration success, but margining info were missing. Once the clock driver is setup correctly, everything works fine.

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page