- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

When I send a UDP Broadcast packet from the PC to the board, the packet is

visible on the GMII RX lines coming from PHY. But data do only sporadically arrive on the Avalon-ST RX bus - see post TSE GMII gmii_rx_dv without data_rx_valid signal

The behaviour depends on the synthesis - without logic reference. Sometimes it works, sometimes it doesn't work and I have to resynthesise. This is annoying, so I would like to have a consistent solution to the problem.

The FPGA C10GX200 with the MAC TSE IP Core is connected to a PHY KSZ9031MNX.

Fifoless TSE MAC without Nios.

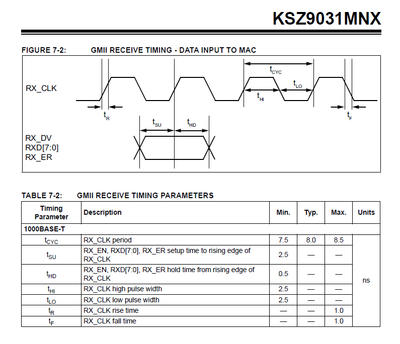

For the KSZ9031MNX PHY the GMII receive timing - data input to MAC is given as follows:

I understand that the phy applies the data on the falling rx_clock edge. Correct?

Or do I have to take care of this delay myself for the incoming data in the FPGA?

I have tried around with the following instructions and different delay times in the sdc file of the project. There seems to be an influence on the behaviour described above, but maybe that's just coincidence, because the problem still occurs in a synthesis-dependent way.

set_input_delay -clock rx_clk -rise 2.000 eth_rx_dv

set_input_delay -clock rx_clk -rise 2.000 eth_rx_err

set_input_delay -clock rx_clk -rise 2.000 eth_rxd[*]

I found the sdc file attached (altera_eth_tse_fifoles_mac.sdc) in the directory of the TSE IP core, but I don't quite understand what it does and whether it has an effect on my problem.

Unfortunately, there is very little information about timing in the TSE IP Core documentation.

Is there a more detailed instruction for this somewhere?

What does the timing have to look like so that the TSE IP Core reliably outputs the received data to the Avalon-ST bus?

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Thank you for using Intel Communities. Please allow some time while I investigate your problem.

In the meantime, is it possible for you to share an isolated design containing the TSE IP?

Thanks,

Regards,

Nurina

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

You find the IP Core attached.

Do you have a mailbox address?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

I have sent you an email. You may share your design there.

Please find the email subject "Intel Customer Support - Case #: 06005652"

Please let me know which Quartus version you are using as well.

Thanks,

Nurina

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Found the cause:

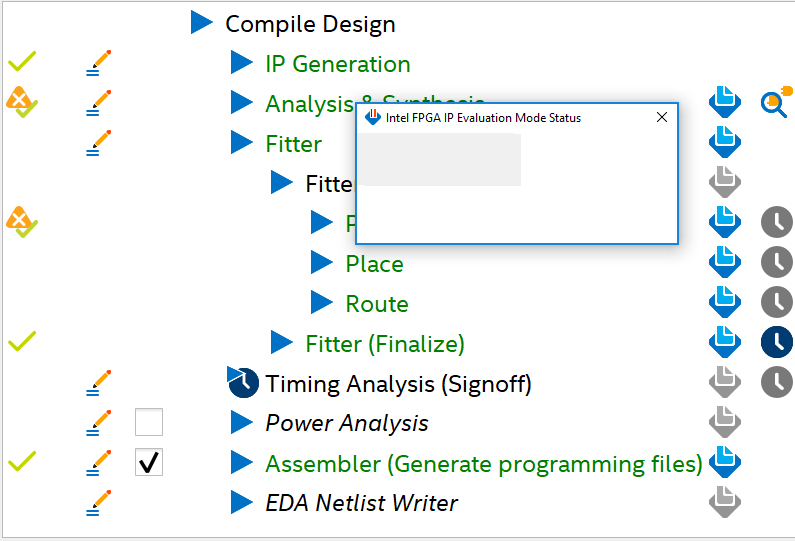

The cause was the licence evaluation dialogue. The dialogue text was not readable on my computer (see figure below) and the window was often hidden behind other open windows.

So I sometimes closed the window and sometimes left it open because I couldn't see it.

When you close the window, the ip core no longer works. - But how can you tell if the dialogue is'nt labelled?

I found the clue here:

community.intel.com/t5/FPGA-Intellectual-Property/TSE-MAC-catatonic/m-p/155152#M12528

Fig. Evaluation dialogue

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

So when you close this window there is a problem with the TSE IP?

May I know which Quartus version you are using and which OS you are using?

Regards,

Nurina

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

We have not received a reply from you. As such, I now transition this thread to community support. If you have a new question, Feel free to open a new thread or login to ‘ https://supporttickets.intel.com ’, view details of the desire request, and post a feed/response within the next 15 days to allow me to continue to support you. After 15 days, this thread will be transitioned to community support. The community users will be able to help you on your follow-up questions.

If any answer from the community or Intel Support are helpful, feel free to rank your support experience by rating 4/5 survey. Please let me know of any inconvenience so that I may improve your future service experience.

Have a great day!

Best regards,

Nurina W.

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page