- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

We want to run the internal ADCs on the 10M25DAF256I7G FPGA.

In this device, there are 2 dedicate analog inputs called "ANAIN1" and "ANAIN2", and 16 pins for analog input or I/O (under bank 1A) called "ADC[1..2]IN[1..8]".

The plan is to use part of the 16 pins as analog input and the other as I/O.

ADC_VREF = 2.5[v]

VCCIO1A = 3.3[v]

Note - In our design, all I/Os should be configured as "3.3-V LVTTL".

Is this design correct?

Thanks.

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

- For 'The plan is to use part of the 16 pins as analog input and the other as I/O'

As mentioned in Intel® MAX® 10 Analog to Digital Converter User Guide:

'If you use bank 1A for ADC, you cannot use the bank for GPIO.'

so other pins cannot be used as I/O.

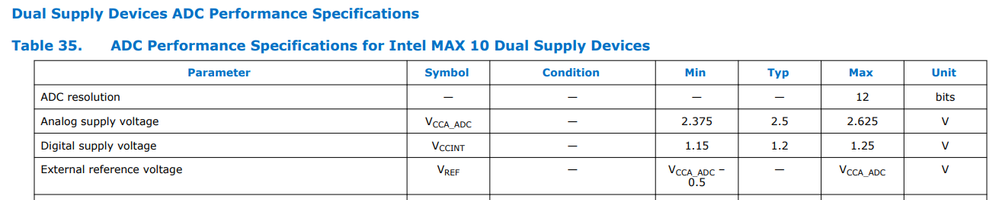

- ADC_VREF = 2.5[v]

That's right.

- VCCIO1A = 3.3[v]

Refer to Intel® MAX® 10 FPGA Device Family Pin Connection Guidelines:

'If you enable the ADC feature, connect VCCIO1A and VCCIO1B to 2.5 V.'

Besides, for ADC, power supply VCCA_ADC and VCCINT are needed.

BR,

Mengzhe

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page