- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

We need to update the SPI Flash used to configure the FPGA fabric of a Cyclone V SoC but the only communication channel available is the ethernet interface.

We can upload the configuration to an external RAM memory.

Is it possible to access this SPI Flash memory directly or with a reconfiguration of the FPGA fabric ?

For information, because we use a SPI flash, the MSEL pins configuration doesn't allow the FPGA manager to reconfigure the FPGA fabric.

Any help appreciated.

Regards,

WabG

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi WabG,

Are you able to load the image from sdcard using the below in order to reconfigure the FPGA fabric?

load mmc 0:1 ${loadaddr} ghrd_10as066n2.core.rbf

fpga load 0 ${loadaddr} ${filesize}

Thanks.

Regards,

Aik Eu

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Aik Eu,

From the Linux's console, I don't have the commands "load" neither "fpga" but this last command seems to use the FPGA manager. I have tried to use the FPGA manager with the "dd" command as described in the figure below :

As the board use an SPI flash to configure the FPGA fabric, the MSEL setting doesn't allow the FPGA manager to configure the FPGA fabric.

Instead of the FPGA manager would it be possible to use the SCAN manager to access the JTAG-TAP controller to configure the SPI flash ?

Regards,

WabG

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

there's no direct access from HPS to FPGA SPI flash. I see two options:

- Implement SPI controller in FPGA fabric and access it through HPS-FPGA bridge. Requires a factory image programmed through JTAG programmer.

- Perform .jic programming from HPS through SCAN manager. Don't know if there are ready-to-use software examples.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

We are thinking about the 2nd solution because we don't have access to the JTAG.

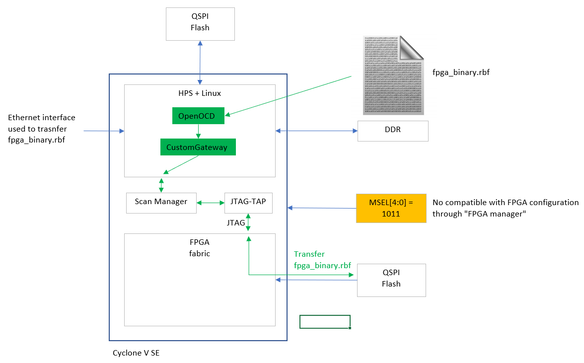

Below would be the solution principle where we use OpenOCD to read the rbf file /send JTAG commands and a custom gateway to capture the OpenOCD command through a virtual port :

Does it looks feasible, any remarks ?

Regards,

WabG

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

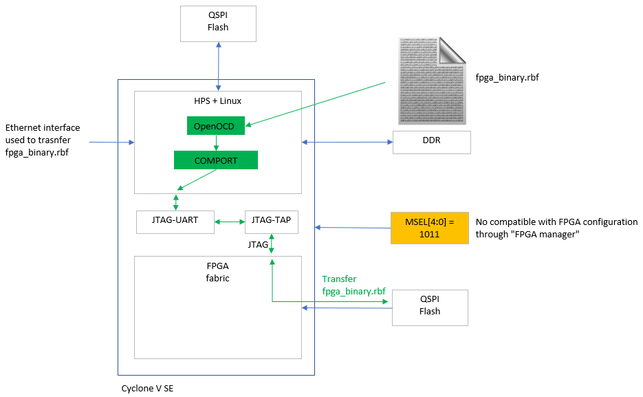

As we have the component JTAG-UART instantiated in the SoC, another solution could be the figure below ?

A pre-requisite would be to configure JTAG-TAP (with scan manager) to not use external pins of JTAG.

What do you think of this solution ?

Regards,

WabG

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi WabG,

For device related boot, we will follow the building bootloader document from rocketboards.

https://www.rocketboards.org/foswiki/Documentation/BuildingBootloaderCycloneVAndArria10

the "fpga load" cmd is only available in Uboot user space but not after enter linux kernel. Remember to perform the "bridge enable" cmd first to have the connection access to FPGA side.

As for your solution which you are looking into, I am not very sure regarding it and I do not see that is common in our support.

Thanks.

Regards,

Aik Eu

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Aik Eu,

So, from UBoot, even with the wrong MSEL pins setting it is possible to configure the FPGA fabric ?

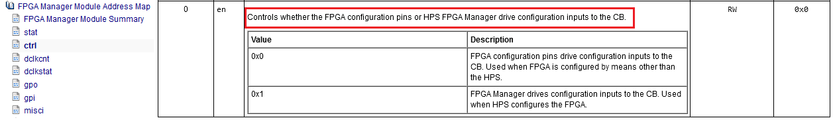

From the documentation, the bit enable of the control register of FPGA manager seems to take control of the FPGA configuration over the MSEL pins, do you confirm ?

Regards,

WabG

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi WabG,

Sorry for the late reply, I am not sure about the combination of settings handling to configure the FPGA fabric on a custom board.

One thing for sure is referring to Cyclone V development kit, booting up with QSPI flash or SD card, the difference will be on BSEL pins only. Then the configuration of FPGA fabric can be done with the same MSEL settings. The configuration of the FPGA fabric is done through Quartus programming tool or in the Uboot User space withe "fpga load". I think can based on the normal configuration settings as a comparison to troubleshoot for your handling on the custom board.

The common documents which we are referring to as below, can check some of the settings handling required:

https://www.rocketboards.org/foswiki/Documentation/BuildingBootloaderCycloneVAndArria10

https://www.rocketboards.org/foswiki/Documentation/CycloneVSoCGSRD

Thanks.

Regards,

Aik Eu

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi WabG,

I am closing this thread and continue the support on the other duplicated thread 06197585. I now transition this thread to community support. If you have a new question, feel free to open a new thread to get the support from Intel experts. Otherwise, the community users will continue to help you on this thread. Thank you.

Thanks.

Regards,

Aik Eu

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page