What steps can I follow to bring up the E-tile PAM4 PMA?

Success! Subscription added.

Success! Subscription removed.

Sorry, you must verify to complete this action. Please click the verification link in your email. You may re-send via your profile.

- Intel Community

- Intel Community Knowledge Base

- Product Support Forums Knowledge Base

- FPGA Knowledge Base

- FPGA Wiki

- What steps can I follow to bring up the E-tile PAM4 PMA?

What steps can I follow to bring up the E-tile PAM4 PMA?

- Subscribe to RSS Feed

- Mark as New

- Mark as Read

- Bookmark

- Subscribe

- Printer Friendly Page

- Report Inappropriate Content

What steps can I follow to bring up PAM4 PMA in Intel® Stratix® 10 FPGA / Intel Agilex® FPGA E-tile design?

Intel® Stratix® 10 FPGA/Intel Agilex® FPGA E-tile PHY requires a bring-up process to ensure normal operating. The PMA bring-up is user-triggered and requires configuring a few registers.

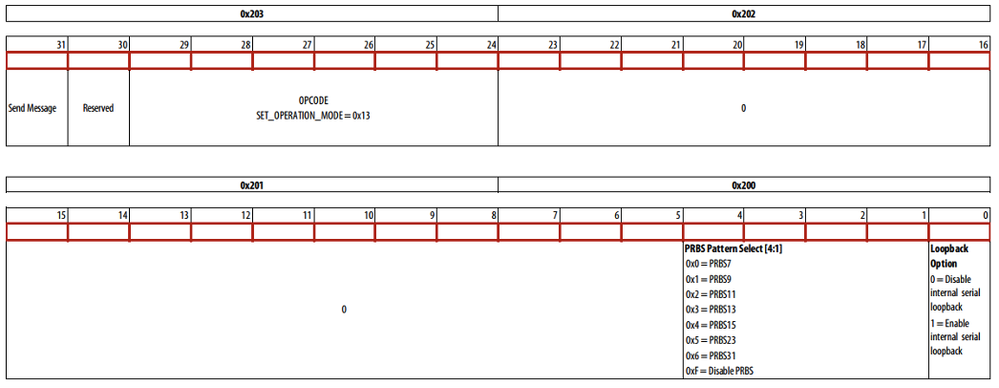

Registers 0x200 to 0x203 could be used to trigger a simple PMA bring-up process, and the steps are as follows.

- Enable PRBS31 and internal serial loopback.

- Write 0x200 = 0x0D (enable PRBS31 and internal serial loopback)

- Write 0x201 = 0x0

- Write 0x202 = 0x0

- Write 0x203 = 0x93 (this picks the opcode for SET_OPERATION_MODE)

- Read 0x207 until it becomes 0x80. This indicates that the operation was completed successfully.

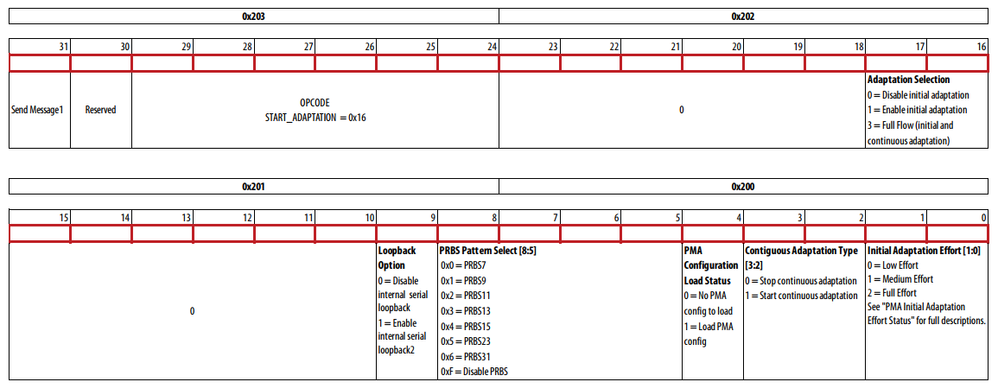

- Run initial adaptation. Enable mission mode, disable internal serial loopback and disable PRBS31.

- Write 0x200 = 0xE1 (medium adaptation effort for PAM4, disable PRBS after adaptation)

- Write 0x201 = 0x01 (disable internal serial loopback after adaptation)

- Write 0x202 = 0x01 (enable initial adaptation)

- Write 0x203 = 0x96 (this picks the opcode for START_ADAPTATION)

- Read 0x207 until it becomes 0x80. This indicates that the operation was completed successfully.

- Check the link status with “rx_is_lockedtodata.”

Loading PMA Configuration Register SET_OPERATION_MODE

Loading PMA Configuration Register START_ADAPTATION

Some extra steps or different register values may be required depending on real transceiver design and link behavior.

- Static temperature flows (STF) and dynamic temperature flows (DTF) have different processes for successful link bring-up.

- If using a PMA configuration, load the PMA configuration is required

- If RX simplex mode is used

- If valid data rate traffic is not available at the RX, rerun initial adaptation until valid traffic is available

You can refer to the Intel E-Tile Transceiver PHY User Guide for further details.

Notices & Disclaimers

Intel technologies may require enabled hardware, software or service activation.

No product or component can be absolutely secure.

Your costs and results may vary.

© Intel Corporation. Intel, the Intel logo, Altera, Arria, Cyclone, Enpirion, MAX, Nios, Quartus

and Stratix, and other Intel marks are trademarks of Intel Corporation or its subsidiaries. Other names and brands may be claimed as the property of others.

The products described may contain design defects or errors known as errata which may cause the product to deviate from published specifications. Current characterized errata are available on request.

The Intel logo, and Intel Agilex are trademarks of Intel Corporation or its subsidiaries

He Zhengmiao (James)

Community support is provided during standard business hours (Monday to Friday 7AM - 5PM PST). Other contact methods are available here.

Intel does not verify all solutions, including but not limited to any file transfers that may appear in this community. Accordingly, Intel disclaims all express and implied warranties, including without limitation, the implied warranties of merchantability, fitness for a particular purpose, and non-infringement, as well as any warranty arising from course of performance, course of dealing, or usage in trade.

For more complete information about compiler optimizations, see our Optimization Notice.