- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

We are 100% new to Quartus (and FPGA in general). I have a project (the DE1-SoC Computer System that comes by default with the University Program when using NIOS II), that I would like only to change the .qsf file with a couple of small changes and synthesize it to run in the DE1-SoC. These changes are just remapping the switches to some GPIOs.

When I open the project and synthesize it using Quartus Prime Lite, it ends up generating a file called "DE1_SoC_Computer_time_limited.sof". I successfully run this file but I have to be running the quartus command; which is a problem especially when I want to run also nios2_terminal at the same time.

I have read that I need a license, and that I can request it in: https://licensing.intel.com/psg/s/

But I have no idea what license to request to avoid the time_limited part, or how to apply it. Is it "Intel® FPGA IP IP-NIOSVG"? Is it "Intel® FPGA IP IP-NIOSVM"? Do I have to use the IP Catalog? Is it because of using Quartus Prime Lite?

Thank you so much in advance,

PO

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

do I understand right that you have DE1-SoC board (Cyclone V with ARM SoC). Why do you want to use Nios II soft processor? I guess that your existing design is based on classical Nios II/s core, it requires Quartus Prime Standard (paid license). You might possibly switch to free Nios II/e core. What is your Quartus version?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Greetings and welcome to Intel's forum.

May I know the Quartus version(17.0 or 19.1 etc) you are using? And May I confirm with you the DE1 soc you are using is a Cyclone V with ARM SoC core?

When using the Quartus Prime Web Edition, compiling a design with a Nios II/s or Nios II/f processor will produce a time-limited SOF file. As a result, the board must remain connected to the host computer, and the design cannot be set as the default configuration. Designs using only Nios II/e processors and designs compiled using the Quartus Prime Subscription Edition do not have this restriction.

You may need to request a paid license to use the Quartus Prime STANDARD version and using the Nios II/e core to avoid the time_limited part.

I have here a manual on more information of the DE1-soc Computer for your reference: https://ftp.intel.com/Public/Pub/fpgaup/pub/Intel_Material/18.1/Computer_Systems/DE1-SoC/DE1-SoC_Computer_NiosII.pdf

Hope to hear on your feedback and looking forward to your feedback.

Thank you.

Regards,

Kelly

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi FvM, Kelly,

Thank you for your answers!

Yes: DE1-SoC (Cyclone V with ARM SoC). In the FPGAcademy courses ( https://fpgacademy.org/courses.html ) they support both ARM and Nios and we have to support Nios II. The project I am trying to synthesize is the "University Program" that Intel provides for Nios II on DE1-SoC.

I had read that Nios II/e had some limitations in floating point and I am not sure if these limitations can affect the projects professors work with; so I would prefer, if possible, to stick with the original configuration if possible.

I have just downloaded the Quartus Prime Standard 22.1std.1 with the 90-day evaluation license, but I see that this also generated the DE1_SoC_Computer_time_limited.sof file. In theory with the Standard version it should be enough, or do I need any further license of an IP or similar?

Thank you!

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Thank you for your feedback.

Unfortunately, the DE1_SoC_Computer project is a default design example, you can only use the Nios II/e core to avoid the time_limited part as stated from the manual.

Yes, the Nios II/e core will have some floating point limitations, but you may change the core to a fast core for other projects you wish to compile.

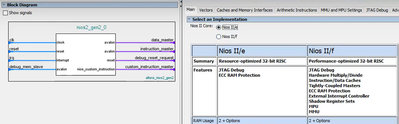

I have attached a screenshot on the NIOS II processors (e and f) for your reference where you are able to change.

Hope this clarify your doubts.

Thank you.

Regards,

Kelly

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Attached here is a screenshot on how to change the cores to fast or economy for the DE1 SoC based on your project needs after you have selected NIOS II processor on Platform Designer:

Thank you.

Regards,

Kelly

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Any updates from you end whether the feedback provided is useful?

Thank you.

Regards,

Kelly

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Any updates from you end whether the feedback provided is useful?

Thank you.

Regards,

Kelly

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

As we do not receive any response from you on the previous question/reply/answer that we have provided. Please login to ‘https://supporttickets.intel.com’, view details of the desire request, and post a feed/response within the next 15 days to allow me to continue to support you. After 15 days, this thread will be transitioned to community support. The community users will be able to help you on your follow-up questions.

p/s: If any answer from the community or Intel Support are helpful, please feel free to give best answer or rate 4/5 survey.

Thank you.

Regards,

Kelly Jialin, GOH

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page