- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello

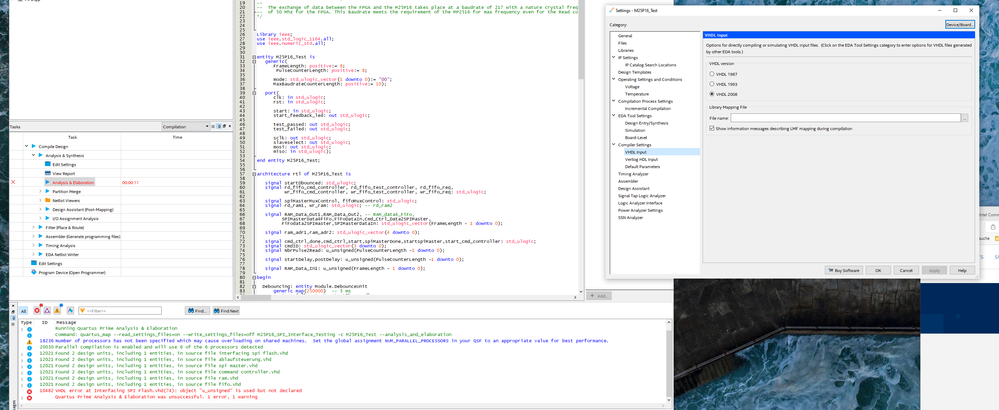

I can't handle a ccompilation Error on Quartus 20.1 Lite.

As you can see in the screenshot. Quartus have some problem with my code at the line74.

I'm declaring an unresolved signal at this line. Previously I had include the package numeric_std at the line 28 where this type is defined. Hence I have no clue what is goeing wrong here from Quartus.

In addition to all this, I have to mention that i have selected vhdl 2008 in the compiler Settings as you can in the scrrenhot, and that I have already compile and simulate my design on Modelsim Altera.

If there is someone who can help me here. I would be thankfull

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

What is u_unsigned? Do you mean to_unsigned?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

It's the alias for unresolved unsigned.

Here is the declaration of this type in the quartus numeric_std package as i found it in the file numeric_std_vhdl2008 from quatus vhdl library file:

type UNRESOLVED_UNSIGNED is array (NATURAL range <>) of STD_ULOGIC;

type UNRESOLVED_SIGNED is array (NATURAL range <>) of STD_ULOGIC;

alias U_UNSIGNED is UNRESOLVED_UNSIGNED;

alias U_SIGNED is UNRESOLVED_SIGNED;

subtype UNSIGNED is (resolved) UNRESOLVED_UNSIGNED;

subtype SIGNED is (resolved) UNRESOLVED_SIGNED;

I have the same error even if I used the complete type name instead of the alias

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Quartus, especially Lite and Standard, has pretty limited VHDL2008 support (check the built-in help for what's supported). That might be what you're running into here.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

As mentioned here: https://www.intel.com/content/dam/www/programmable/us/en/pdfs/literature/po/ss-quartus-comparison.pdf

Quartus lite/standard has limited supported in Systemverilog VHDL2008. I would recommend to run in Quartus Pro. or to change to Verilog language.

Best Regards,

Richard Tan

p/s: If any answer from the community or Intel support are helpful, please feel free to give Kudos.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

The question is about VHDL2008, not Verilog or SystemVerilog.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I have yet to receive any response from you to the previous question/reply/answer that I have provided but I believed that I have answered your question.

With that, I will now transition this thread to community support. If you have a new question, feel free to open a new thread to get the support from Intel experts. Otherwise, the community users will continue to help you on this thread. Thank you.

Best Regards,

Richard Tan

p/s: If any answer from the community or Intel support are helpful, please feel free to give Kudos.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello Richard,

Sorry for the late reaction. It's difficult for me to give a feedback here since i have right now experienced a very twisted situation with Quartus Lite.

Following the discussion here about the limited support for VHDL 2008, I decide to use instead of unresolved_unsigned type an unsigned type signal. Although the unsigned type is defined as a subtype of unresolved_unsigned, the compilation error that I had was solved.

However I still could not compile my design on quartus because it has now a problem with the simple shift right operator sra.

The compiler can not find a definition for this operator with operands of type unsigned or std_ulogic_vector although this operator is defined in the package NUMERIC_STD from Quartus in the data numeric_std_unsigned_vhdl2008.vhdl with operands of type unresolved_unsigned and in the package numeric_std_unsigned with the operands of type std_ulogic_vector.

Now I have no clue what is going wrong here. Do I have an installation related problem or it's solely due to limited vhdl 2008 support?

I'm disappointed because i'm expecting from any eda tool supporting vhdl design, a very simple support for basic operators as logical operators here, shifting operators.

So If there are users who experience similar problems, I will be very happy to read from them.

Best Regards

Ludovic

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I think you're supposed to use shift_right instead of sra.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Thanks, As soon as I will test you proposition, I will give a feedback.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello Everyone here,

I finally could compile and get a synthesized design.

Thanks a lot for your advice

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page